# Semiconductors for Wired Telecom Systems

1997

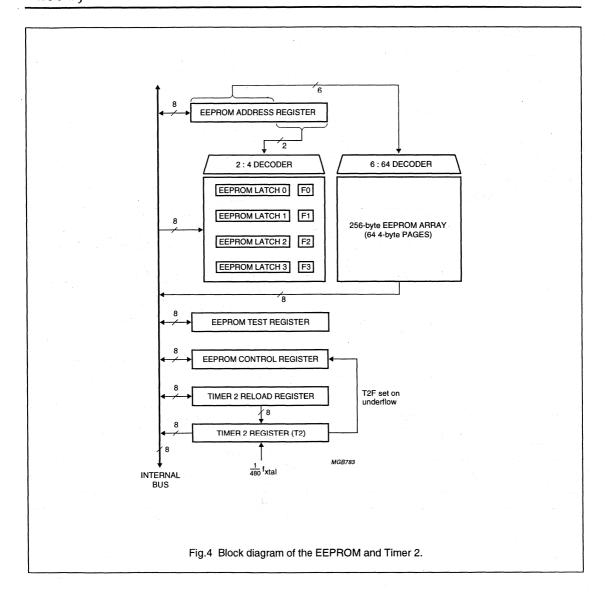

Data Handbook IC03a

Let's make things better.

**PHILIPS**

# **QUALITY ASSURED**

Our quality system focuses on the continuing high quality of our components and the best possible service for our customers. We have a three-sided quality strategy: we apply a system of total quality control and assurance; we operate customer-oriented dynamic improvement programmes; and we promote a partnering relationship with our customers and suppliers.

## PRODUCT SAFETY

In striving for state-of-the-art perfection, we continuously improve components and processes with respect to environmental demands. Our components offer no hazard to the environment in normal use when operated or stored within the limits specified in the data sheet.

Some components unavoidably contain substances that, if exposed by accident or misuse, are potentially hazardous to health. Users of these components are informed of the danger by warning notices in the data sheets supporting the components. Where necessary the warning notices also indicate safety precautions to be taken and disposal instructions to be followed. Obviously users of these components, in general the set-making industry, assume responsibility towards the consumer with respect to safety matters and environmental demands.

All used or obsolete components should be disposed of according to the regulations applying at the disposal location. Depending on the location, electronic components are considered to be 'chemical', 'special' or sometimes 'industrial' waste. Disposal as domestic waste is usually not permitted.

# Semiconductors for Wired Telecom Systems

# CONTENTS

|                                        | Page |

|----------------------------------------|------|

| PREFACE                                | 3    |

| SELECTION GUIDE                        | 5    |

| GENERAL                                | 27   |

| APPLICATION NOTES SUMMARIES            | 41   |

| DEVICE DATA (in alphanumeric sequence) | 57   |

| PACKAGE INFORMATION                    | 873  |

| DATA HANDBOOK SYSTEM                   | 898  |

## **DEFINITIONS**

| Data sheet status         |                                                                                                                                                                               |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | This data sheet contains target or goal specifications for product development.                                                                                               |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later.                                                                                         |

| Product specification     | This data sheet contains final product specifications.                                                                                                                        |

| Short-form specification  | The data in this specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook |

## **Limiting values**

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

## **Application information**

Where application information is given, it is advisory and does not form part of the specification.

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

## PURCHASE OF PHILIPS I2C COMPONENTS

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specification defined by Philips. This specification can be ordered using the code 9398 393 40011.

### **PREFACE**

Thank you for your interest in wired telecom products from Philips Semiconductors. As a leading supplier to the telephony market, we offer a wide range of discrete and integrated semiconductor telecom components.

## A DETAILED REFERENCE SOURCE

This wired telecom handbook includes information on Philips Semiconductors current integrated circuits and discrete products for wired applications. The products offer a comprehensive solution for wired telephony terminals, from line-interfaces, tone and pulse diallers and discrete devices though to hands-free circuits and LCD drivers.

To make selection easier, information is grouped into sections, each accompanied by a product selector guide, which describes the most significant product features. Each section contains detailed product descriptions in the form of data sheets.

Relevant application notes are published in the Application Handbook for Wired Telecom Systems (IC03b). Together IC03 part a) and b) provides a comprehensive reference source for wired telephony, including not only details about Philips Semiconductors products, but also how best to apply them. Summaries of the application notes available for wired telecom systems are on page 41, which also indicates how to order the application handbook (IC03b)

### **COMPREHENSIVE SOLUTIONS**

Philips Semiconductors is a recognised leader in enabling technologies, system-level Know-How, silicon, software and product development resources to help customers take full advantage of one of the fastest growing markets in the world. Specifically the company is a leading innovator of products for:

- · Speech and Transmission circuits.

- · Listening-in and hands-free circuits.

- · Diallers and DTMF generators.

- Derivative telephony-specific micro-controllers; the largest range of configurations and performance options, including low-voltage devices operating down to 1.8V.

- Low-voltage one-time-programmable (OTP) devices, including the PCD3755/56, the lowest-voltage OTP on the

market!

- · Bipolar transistors, regulators and protection diodes.

- LCD display drivers (available additionally as naked die or as chip-on-glass module assemblies).

### **TECHNOLOGY LEADER**

Implementation of cost-effective Telecom terminals demands a broad knowledge, not only at the systems level, but also at the interconnection and component level. Philips Semiconductors state-of-the art fabrication and packaging expertise provides the technology needed for today's demanding applications, together with the reliability and quality levels customers have come to rely upon from one of the world's top-ten semiconductor companies.

### **UNRIVALLED RESOURCES**

Philips Semiconductors has one of the widest portfolios of technology in Semiconductors to meet the needs of the wired telephony market. World-class designs, advanced fabrication processes and up-to-date manufacturing plans and logistics has established Philips Semiconductors as a world supplier. Quality Assurance is based on internationally-accepted quality standards such as ISO9000 as well as customer-specific standards such as Ford's TQE - awarded to Philips Semiconductors in 1995, and AT&T's 'Partner in Excellence' award in 1995, which will honour only five suppliers (including only two semiconductor suppliers) this year.

### **CUSTOMER CO-OPERATION**

Co-operation with customers is vital for securing market acceptance of customers' products and our own. In addition, we believe that technical partnerships are extremely important for stimulating further development of advanced Telecom technology, and have successful partnerships with major Telecom systems suppliers and terminal makers.

### WORLD-WIDE RESEARCH AND DESIGN-IN SUPPORT

Over 18 per cent of our turnover is invested back into research and development, covering process technology, design, system innovation, type/product development and assembly technology. The result is over 300 new devices per year, along with new technology and process developments, software and services.

We have our own divisional PCALs (Product Concept and Application Laboratories), which explore new uses and applications; act as design and development laboratories to uncover potential problems from customers and help them develop their products faster through shared development; and replicate customer engineering efforts in-house.

Product development teams located at our manufacturing and development sites are technology-oriented. Many of our new products are the direct result of work done by the development teams, working alone, or in conjunction with groups in the Research or Applications Laboratories.

# **Philips Corporate Research Labs**

Eindhoven, The Netherlands Redhill, UK Limeil-BrÈvannes, France Aachen/Hamburg, Germany Briarcliff Manor, USA

# **Philips System Labs**

Taipei, Taiwan

In construction

Eindhoven, The Netherlands

TV, Telephony, Micro-controllers

Southampton, UK

Teletext, digital audio, software for TV and CD-ROM

Hamburg, Germany

Automotive, identification, DSP in radio and TV,

Multimedia

Sunnyvale, USA

Multimedia, datacom, automotive

# **Product Development Teams**

Caen, France

Speech and Transmission circuits, hands-free Ics

Zürich, Switzerland

Telecom Microcontrollers, LCD drivers, peripheral Ics

Hamburg, Germany

Nijmegen, The Netherlands

Stadskanaal, The Netherlands

Discrete semiconductors and regulators

# **SELECTION GUIDE**

|                    | Page |

|--------------------|------|

| Functional index   | 6    |

| Alphanumeric index | 9    |

| Replacement list   | 12   |

| Selection lists    | 15   |

# **Functional index**

# Selection guide

|                       |                                                                                                                 | PAGE |

|-----------------------|-----------------------------------------------------------------------------------------------------------------|------|

| SPEECH/TRANSMISSION   | CIRCUITS                                                                                                        |      |

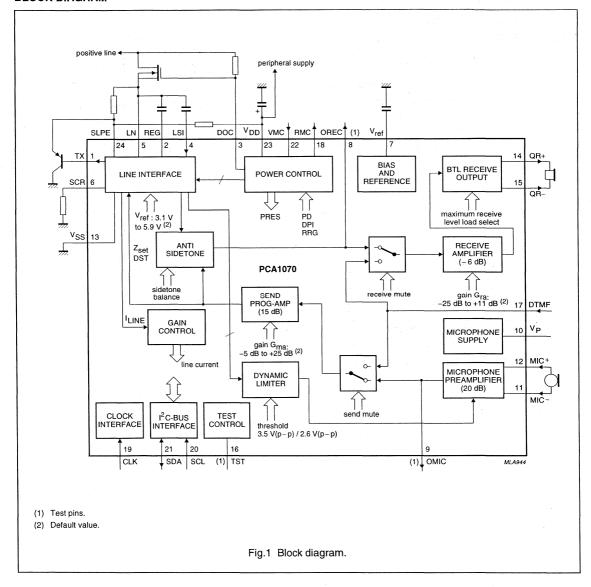

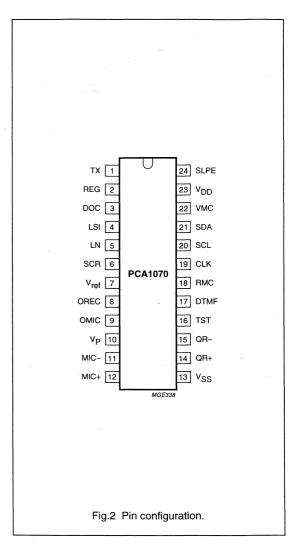

| PCA1070               | Multistandard programmable analog CMOS transmission IC                                                          | 110  |

| TEA1060; TEA1061      | Versatile telephone transmission circuits with dialler interfac                                                 | 483  |

| TEA1062; TEA1062A     | Low-voltage transmission circuit with dialler interface                                                         | 500  |

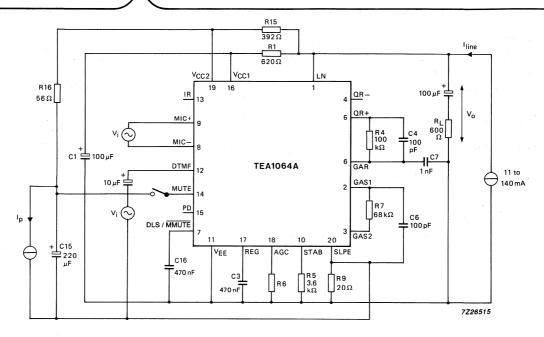

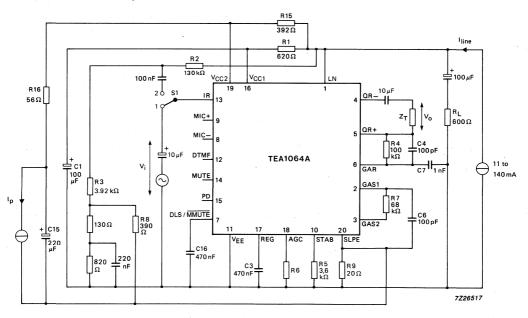

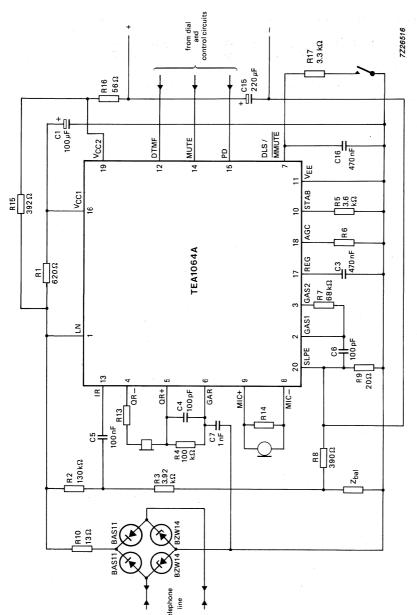

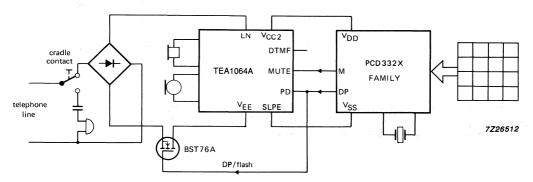

| TEA1064A              | Low voltage versatile telephone transmission circuit with dialler interface and transmit level dynamic limiting | 521  |

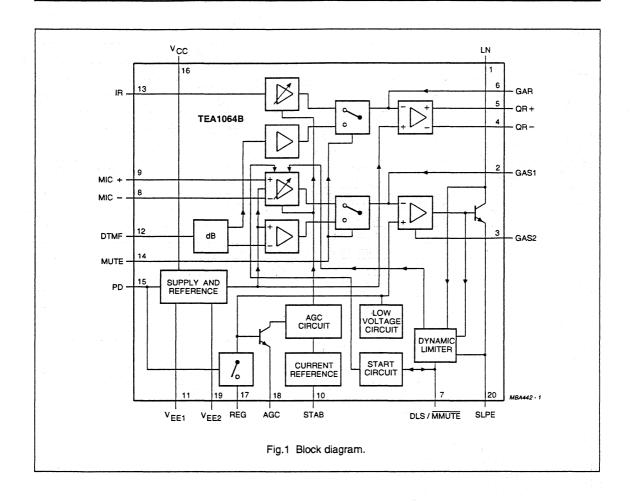

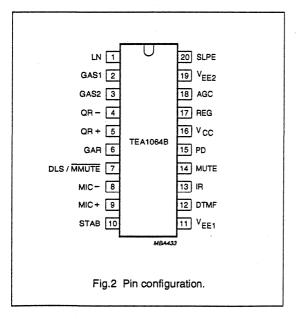

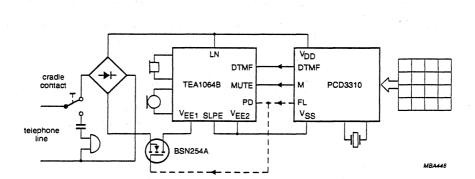

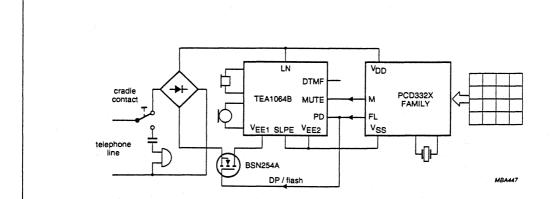

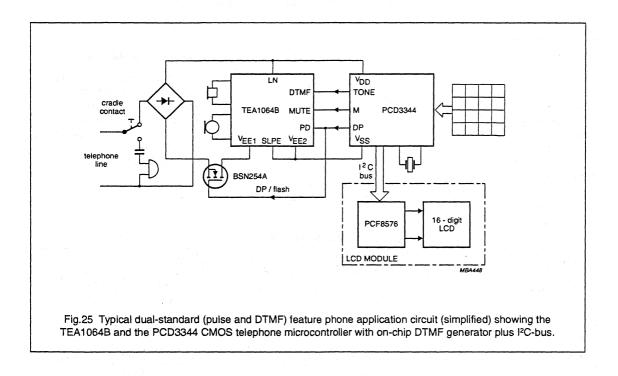

| TEA1064B              | Low voltage versatile telephone transmission circuit with dialler interface and transmit level dynamic limiting | 549  |

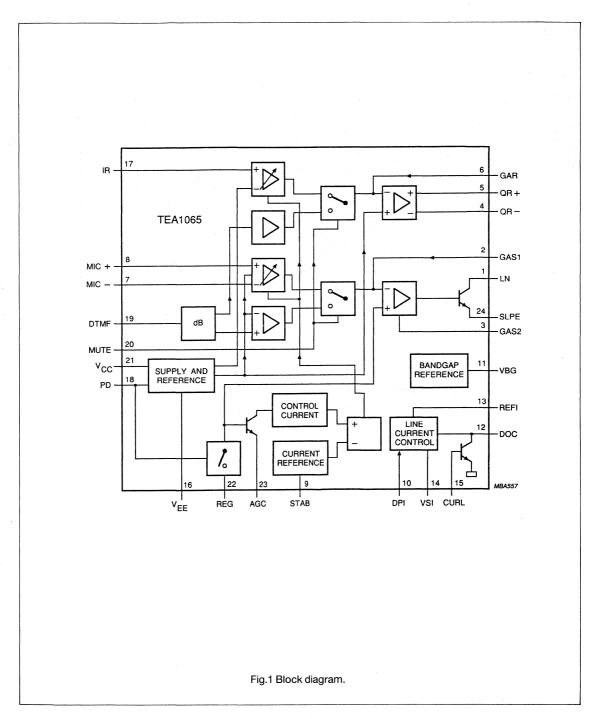

| TEA1065               | Versatile telephone transmission circuit with dialler interface                                                 | 576  |

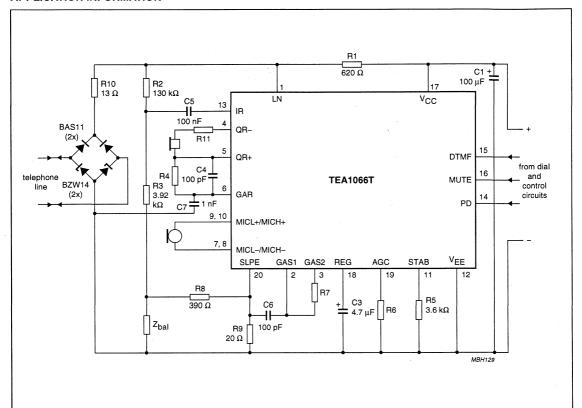

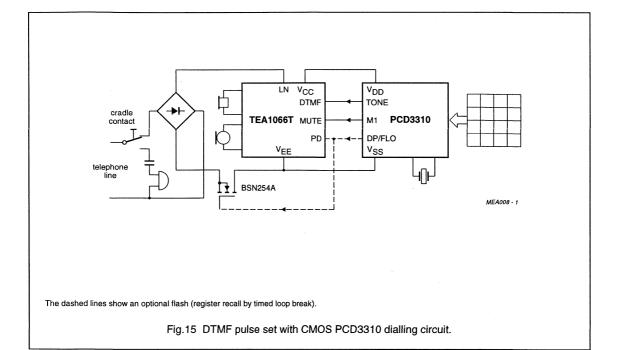

| TEA1066T              | Versatile telephone transmission circuit with dialler interface                                                 | 595  |

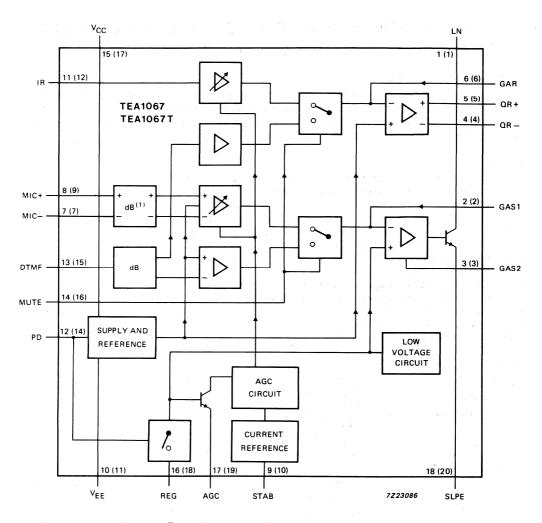

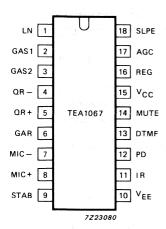

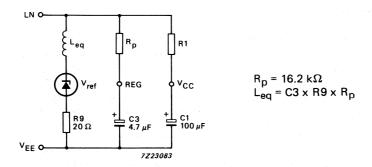

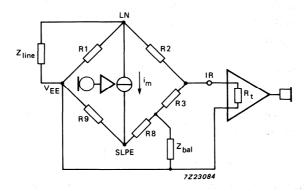

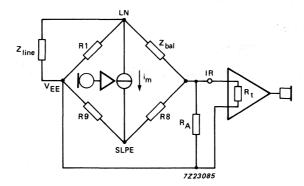

| TEA1067               | Low voltage versatile telephone transmission circuit with dialler interface                                     | 613  |

| TEA1068               | Versatile telephone transmission circuit with dialler interface                                                 | 632  |

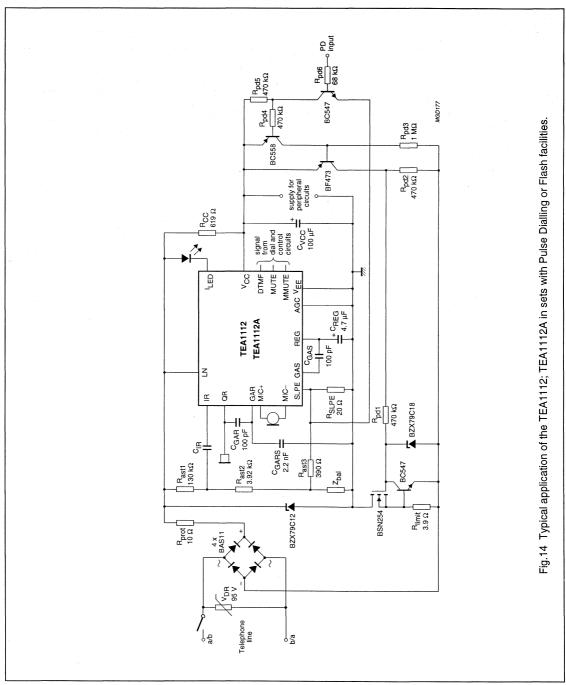

| TEA1112; TEA1112A     | Low voltage versatile transmission circuits with dialler interface                                              | 802  |

| TEA1113               | Low voltage versatile telephone transmission circuit with dialler interface                                     | 821  |

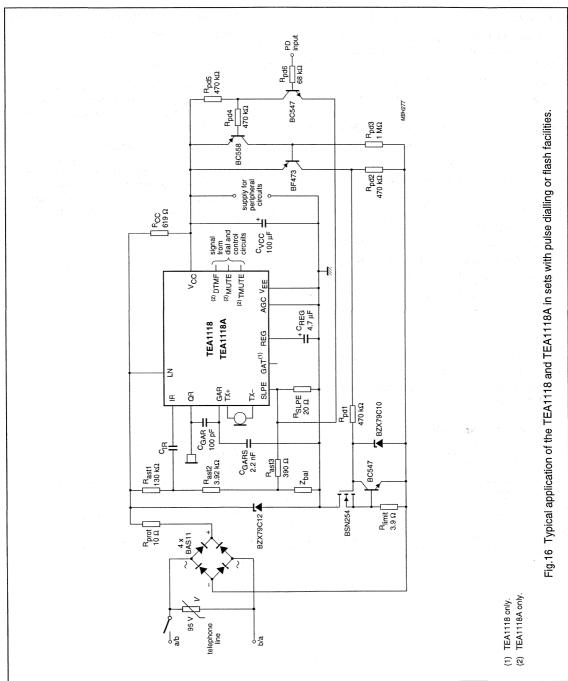

| TEA1118; TEA1118A     | Versatile cordless transmission                                                                                 | 835  |

| LISTENING-IN CIRCUITS |                                                                                                                 |      |

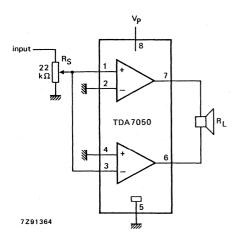

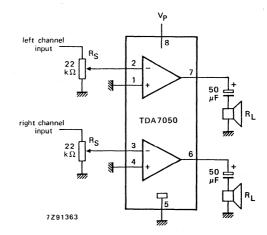

| TDA7050               | Low voltage mono/stereo power amplifier                                                                         | 466  |

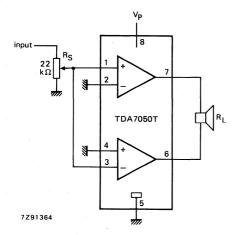

| TDA7050T              | Low voltage mono/stereo power amplifier                                                                         | 471  |

| TDA7052A/AT           | 1 W BTL mono audio amplifier                                                                                    | 475  |

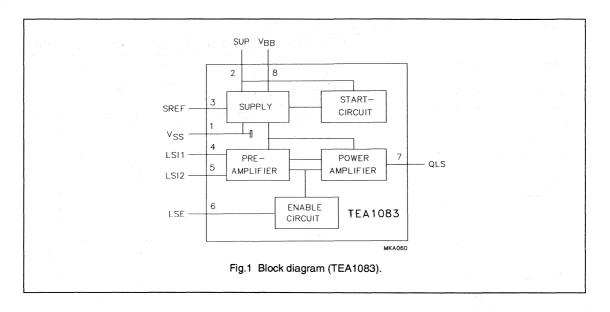

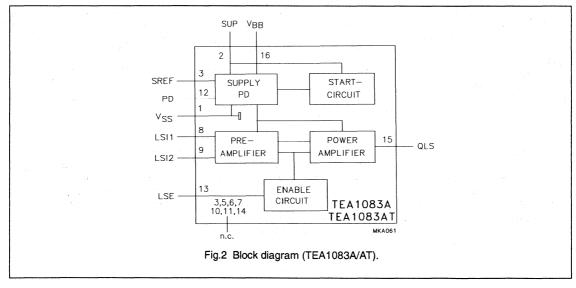

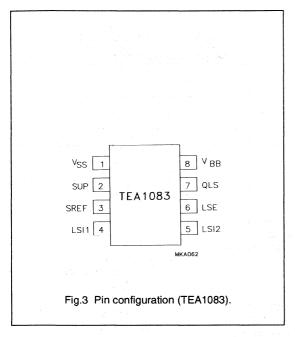

| TEA1083; TEA1083A     | Call progress monitor for line powered telephone sets                                                           | 682  |

| TEA1085; TEA1085A     | Listening-in circuit for line powered telephone sets                                                            | 699  |

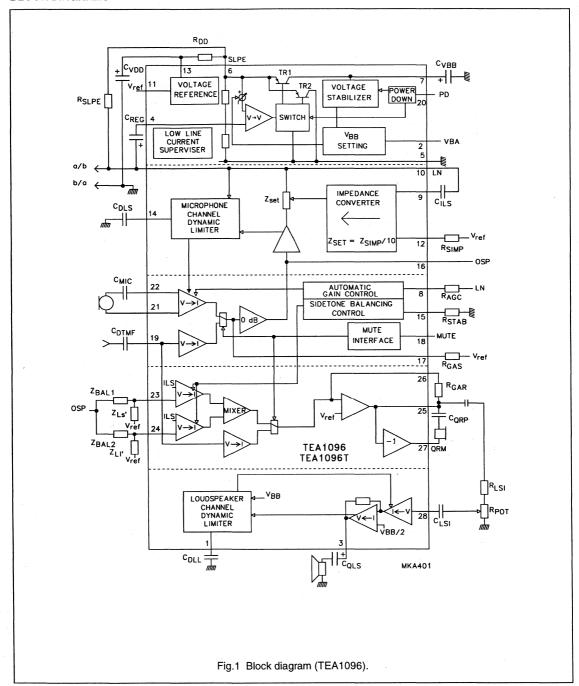

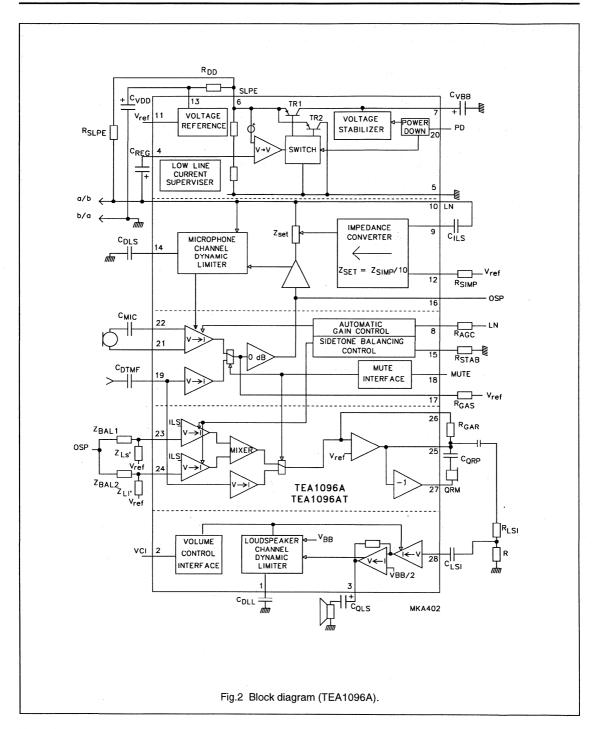

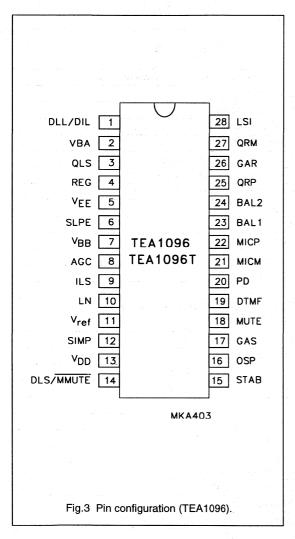

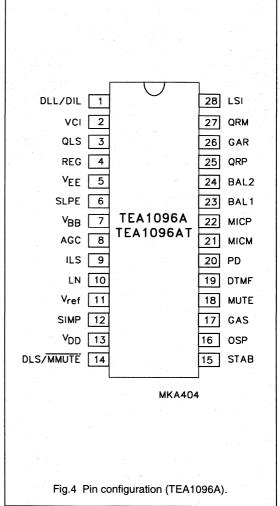

| TEA1096; 1096A        | Speech and listening-in IC                                                                                      | 781  |

| HANDS-FREE CIRCUITS   |                                                                                                                 |      |

| TEA1093               | Hands-free IC                                                                                                   | 722  |

| TEA1094; TEA1094A     | Hands-free IC                                                                                                   | 744  |

| TEA1095               | Noise switched speakerphone IC                                                                                  | 763  |

| SINGLE-CHIP TELEPHON  | IE IC                                                                                                           |      |

| TEA1069N              | Versatile speech/dialler/ringer with music-on-hold                                                              | 649  |

| DIALLERS AND DTMF GE  | ENERATORS                                                                                                       |      |

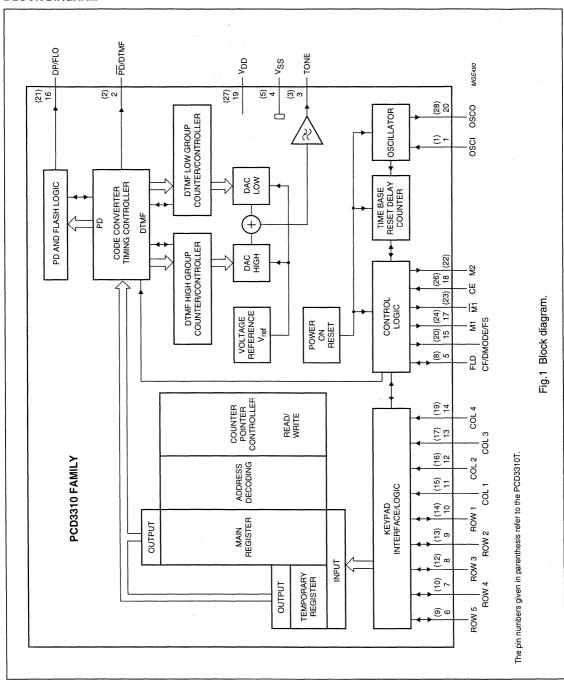

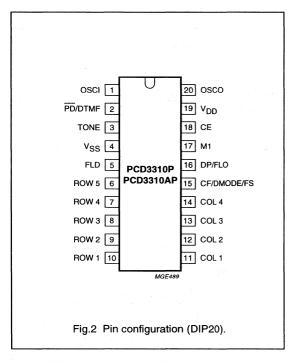

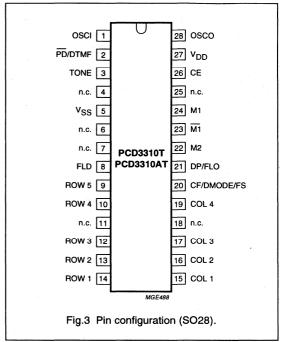

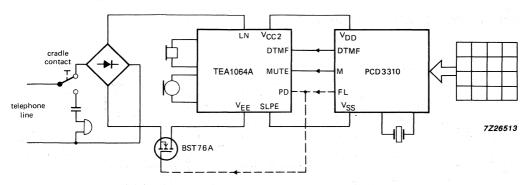

| PCD3310 family        | Pulse and DTMF dialler with redial                                                                              | 141  |

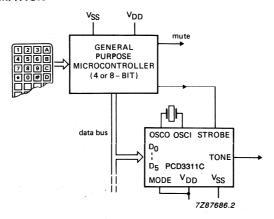

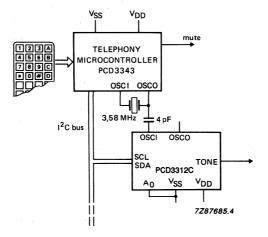

| PCD3311C; PCD3312C    | DTMF/modem/musical-tone generators                                                                              | 154  |

| PCD3330               | Multistandard repertory dialler/ringer with EEPROM                                                              | 176  |

| PCD3332-X family      | Multistandard pulse/tone repertory dialler/ringer                                                               | 179  |

1996 Aug 19 6

Functional index Selection guide

|                                       |                                                                                    | PAGE |

|---------------------------------------|------------------------------------------------------------------------------------|------|

| COMPLEMENTARY PRODU                   | JCTS                                                                               |      |

| NE/SE567                              | Tone decoder/phase-locked loop                                                     | 90   |

| NE5900                                | Call progress decoder                                                              | 103  |

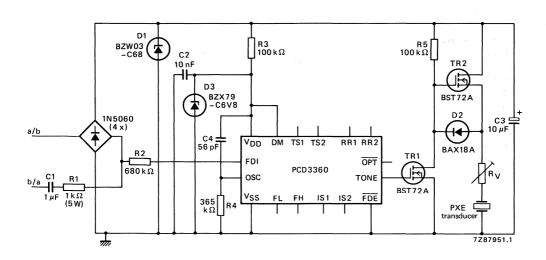

| PCD3360                               | Programmable multi-tone telephone ringer                                           | 321  |

| PCD4440T                              | analog voice scrambler/descrambler                                                 | 411  |

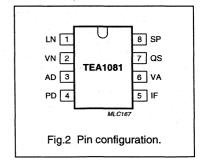

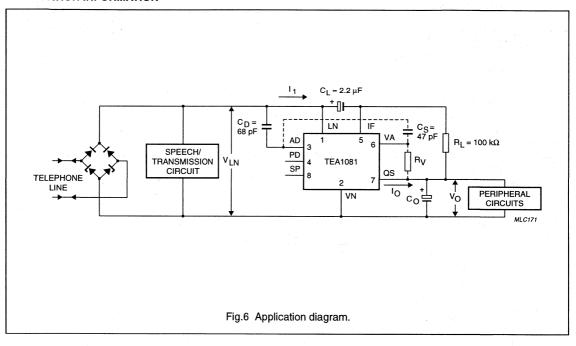

| TEA1081                               | Supply circuit with power-down for telephone set peripherals                       | 680  |

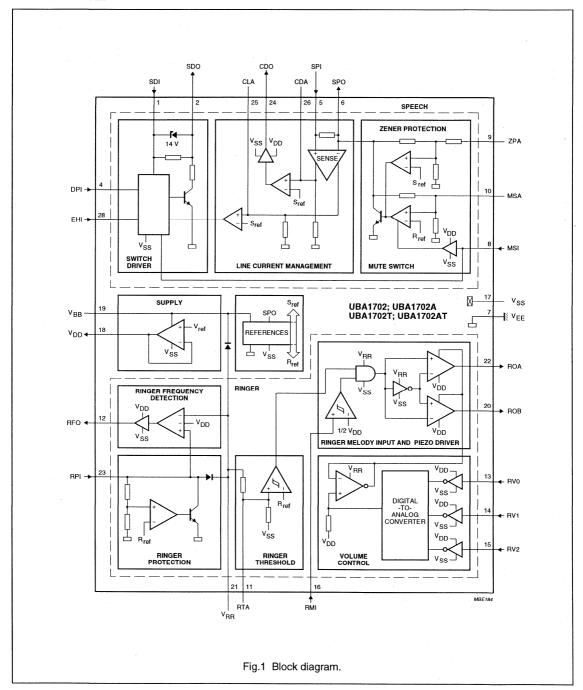

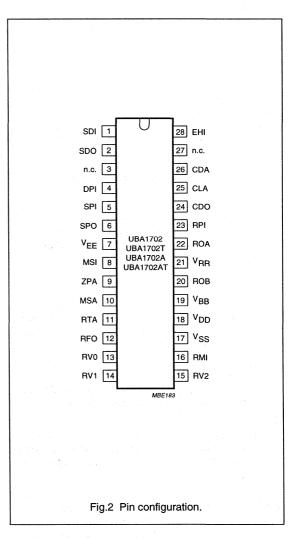

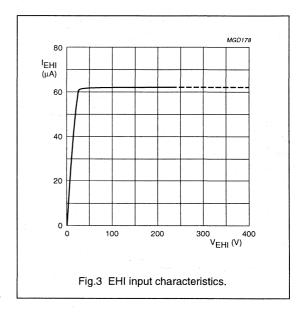

| UBA1702; UBA1702A                     | Line interrupter driver and ringer                                                 | 850  |

|                                       |                                                                                    |      |

| MICROCONTROLLERS                      |                                                                                    |      |

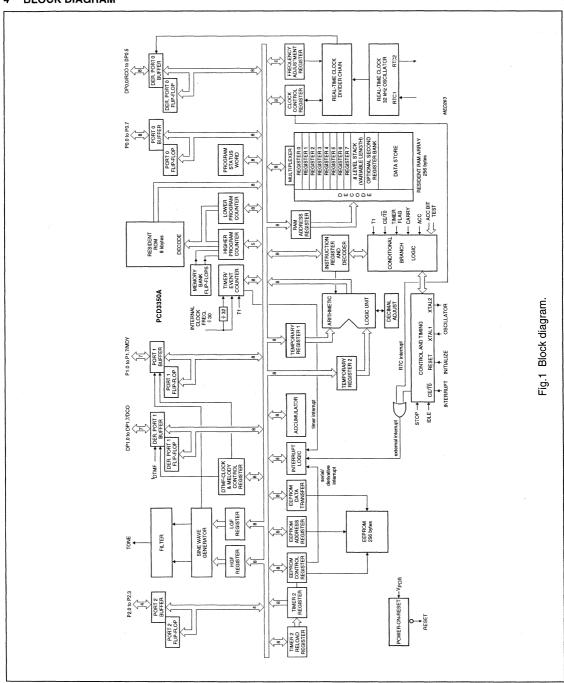

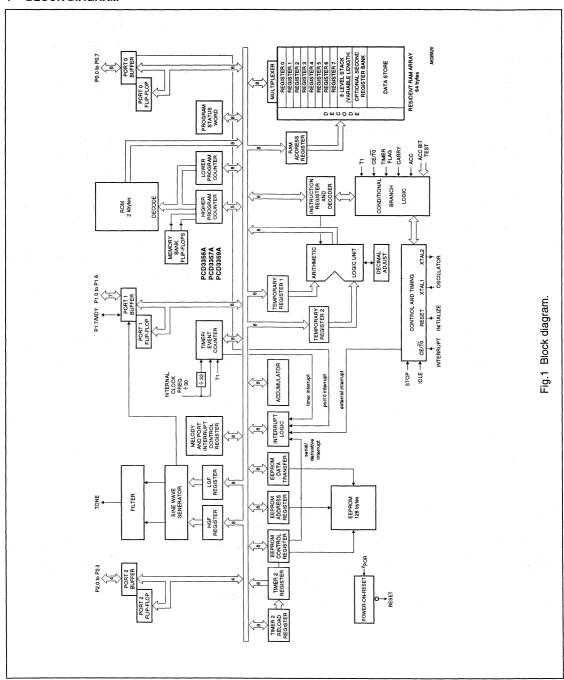

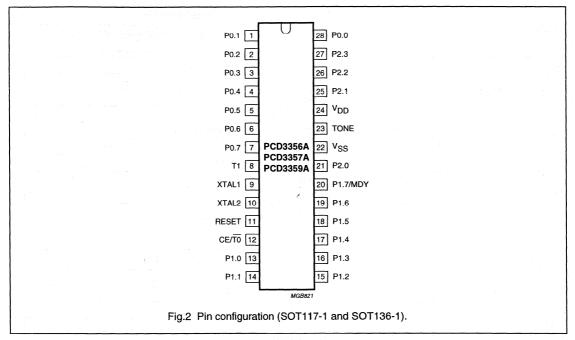

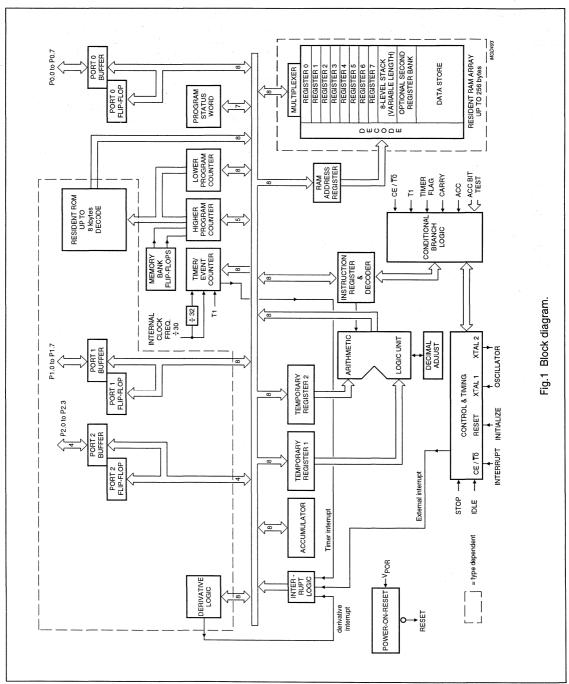

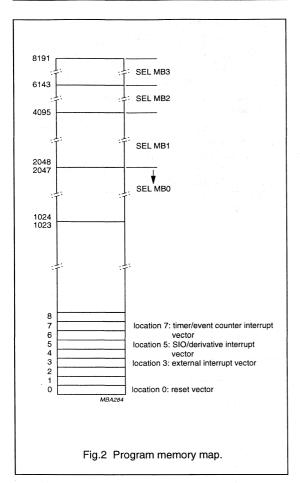

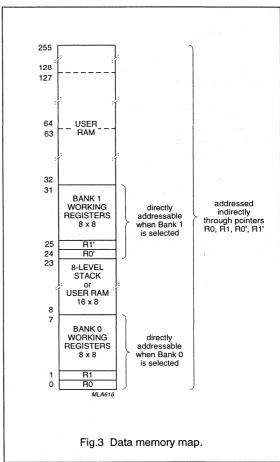

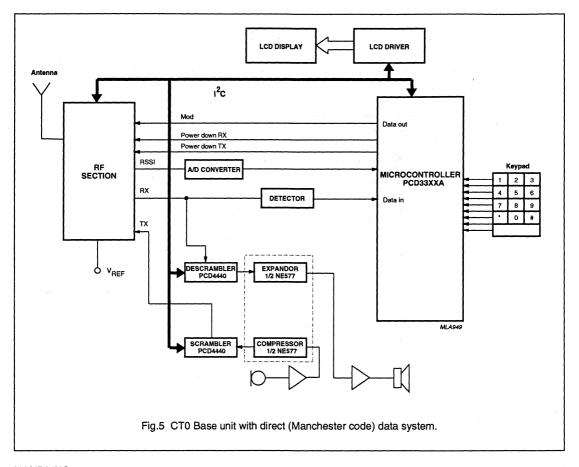

| PCD33XXA family                       | 8-bit telecom microcontroller                                                      | 334  |

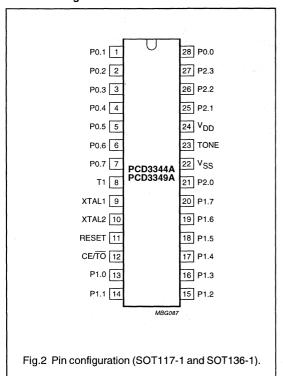

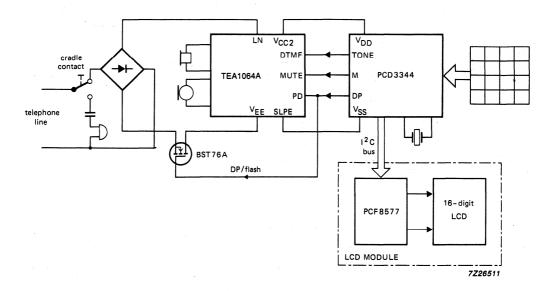

| PCD3344A; PCD3349A                    | 8-bit microcontroller with DTMF generator                                          | 201  |

| PCD3350A                              | 8-bit microcontroller with DTMF generator and 256 bytes EEPROM and real-time clock | 215  |

| PCD3351A/52A/53A;<br>PCA3351C/52C/53C | 8-bit microcontroller with DTMF generator and 128 bytes EEPROM                     | 246  |

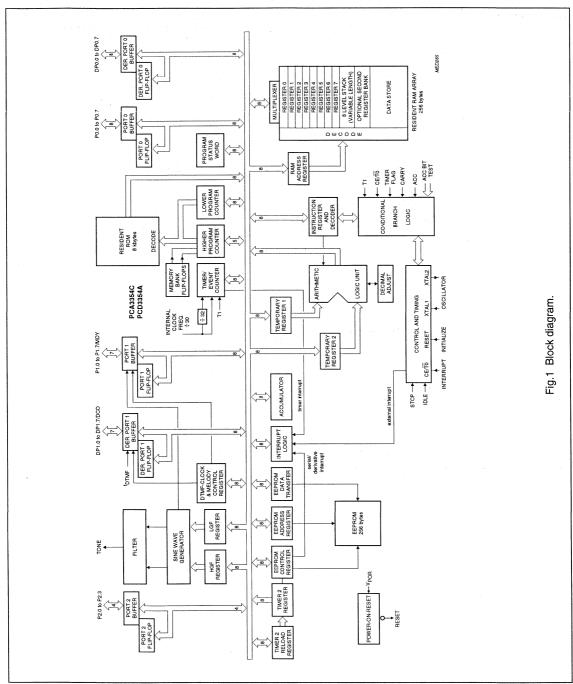

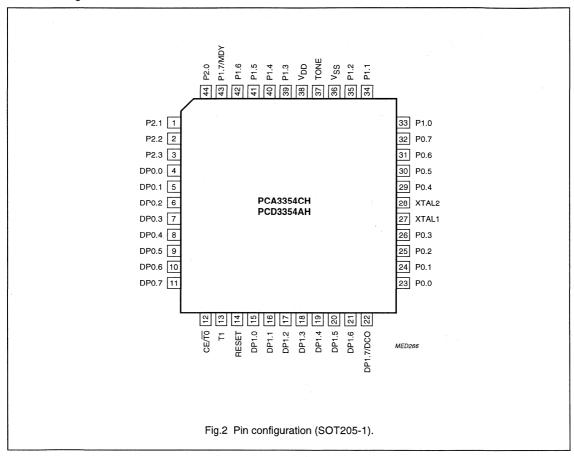

| PCD3354A/54C                          | 8-bit microcontroller with DTMF generator and 256 bytes EEPROM                     | 271  |

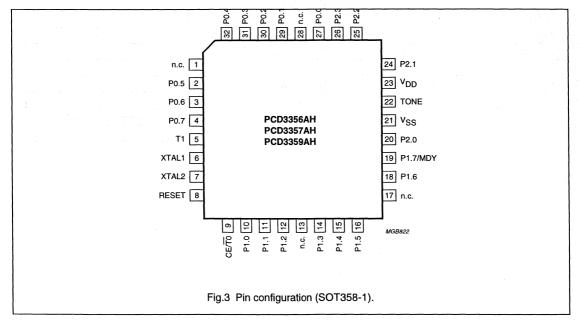

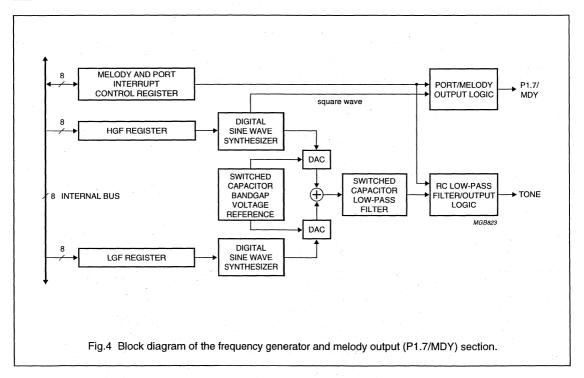

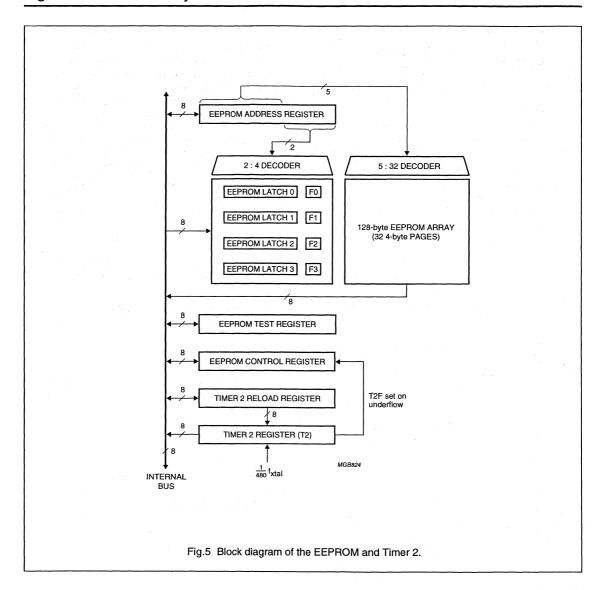

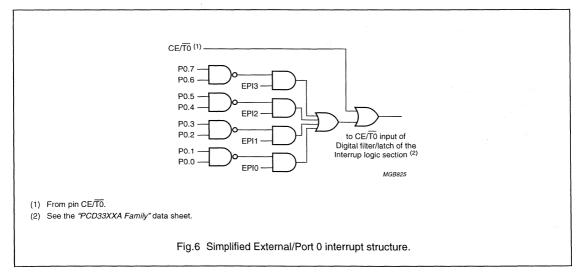

| PCD3356A/57A/59A                      | 8-bit microcontroller with DTMF generator and 128 bytes EEPROM                     | 296  |

| PCD3755X                              | 8-bit microcontroller with DTMF generator, 8 kbytes OTP and 128 bytes EEPROM       | 362  |

| PCD3756X                              | 8-bit microcontroller with DTMF generator, 8 kbytes OTP and 128 bytes EEPROM       | 386  |

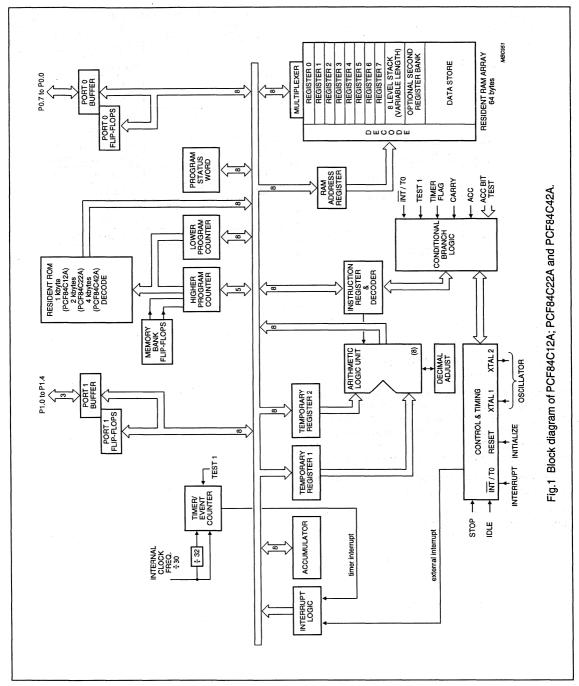

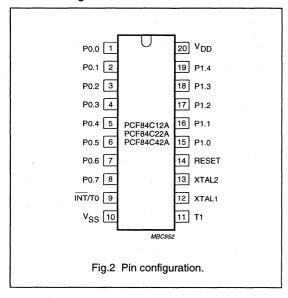

| PCF84C12A/22A/42A                     | 8-bit microcontroller                                                              | 425  |

| BIPOLAR TRANSISTORS,                  | D-MOS-FETs SWICHTES, REGULATOR AND PROTECTION DIODES                               |      |

| 2N5400; 2N5401                        | Silicon PNP high-voltage transistor                                                | 869  |

| 2N5550; 2N5551                        | Silicon NPN high-voltage transistor                                                | 870  |

| 2N7000                                | N-channel enhancement mode vertical D-MOS transistor                               | 871  |

| 2N7002                                | N-channel vertical D-MOS transistor                                                | 872  |

| BC327; BC327A; BC328                  | Silicon planar epitaxial transistor                                                | 58   |

| BC337; BC337A; BC338                  | Silicon planar epitaxial transistor                                                | 59   |

| BC546; BC547; BC548                   | Silicon planar epitaxial transistor                                                | 60   |

| BC556; BC557; BC558                   | Silicon planar epitaxial transistor                                                | 61   |

| BC846; BC847; BC848                   | Silicon planar epitaxial transistor                                                | 62   |

| BC856/7/8                             | Silicon planar epitaxial transistor                                                | 63   |

| BR211 series                          | Breakover diodes                                                                   | 64   |

| BS107                                 | N-channel enhancement mode vertical D-MOS transistor                               | 65   |

| BS107A                                | N-channel enhancement mode vertical D-MOS transistor                               | 66   |

| BS108                                 | N-channel enhancement mode vertical D-MOS transistor                               | 67   |

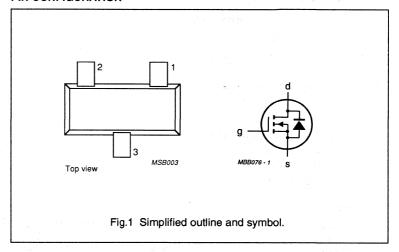

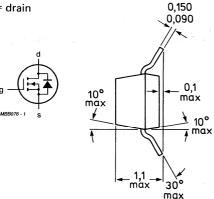

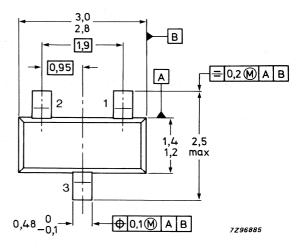

| BS170                                 | N-channel vertical D-MOS transistor                                                | 68   |

| BSN10; BSN10A                         | N-channel enhancement mode vertical D-MOS transistor                               | 69   |

| BSN20                                 | N-channel enhancement mode vertical D-MOS transistor                               | 70   |

7

1996 Aug 19

# Functional index Selection guide

|                                        |                                                       | PAGE |

|----------------------------------------|-------------------------------------------------------|------|

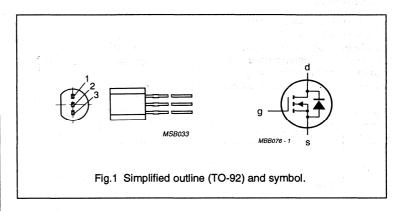

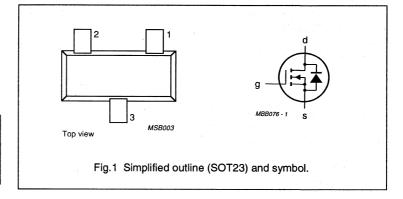

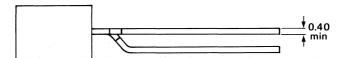

| BSN254; BSN254A                        | N-channel enhancement mode vertical D-MOS transistor  | 71   |

| BSN274; BSN274A                        | N-channel enhancement mode vertical D-MOS transistor  | 72   |

| BSN304; BSN304A                        | N-channel enhancement mode vertical D-MOS transistor  | 73   |

| BSP126                                 | N-channel enhancement mode vertical D-MOS transistor  | 74   |

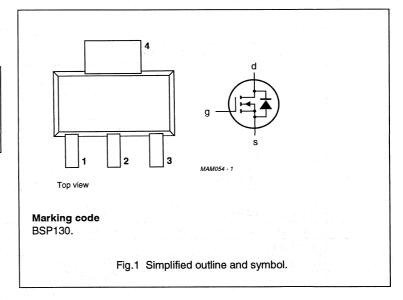

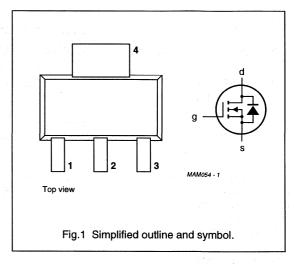

| BSP130                                 | N-channel enhancement mode vertical D-MOS transistor  | 75   |

| BSP145                                 | N-channel enhancement mode vertical D-MOS transistor  | 76   |

| BSP225                                 | P-channel enhancement mode vertical D-MOS transistor  | 72   |

| BSP254; BSP254A                        | P-channel enhancement mode vertical D-MOS transistor  | 78   |

| BSP304; BSP304A                        | P-channel enhancement mode vertical D-MOS transistor  | 79   |

| BSP92                                  | P-channel enhancement mode vertical D-MOS transistor  | 80   |

| BSS89                                  | N-channel enhancement mode vertical D-MOS transistor  | 81   |

| BSS92                                  | P-channel enhancement mode vertical D-MOS transistor  | 82   |

| BST124                                 | N-channel depletion mode vertical D-MOS transistor    | 83   |

| BST74A                                 | N-channel vertical D-MOS transistor                   | 84   |

| BZW03 series                           | Regulator diodes                                      | 85   |

| BZW14                                  | Transient suppressor diode                            | 86   |

| MPSA42; MPSA43                         | High-voltage silicon planar transistor                | 87   |

| MPSA44; MPSA45                         | NPH high-voltage transistor                           | 88   |

| MPSA92; MPSA93                         | High-voltage silicon planar transistor                | 89   |

| PMBF107                                | P-channel enhancement mode vertical D-MOS transistor  | 451  |

| PMBF170                                | N-channel enhancement mode vertical D-MOS transistor  | 452  |

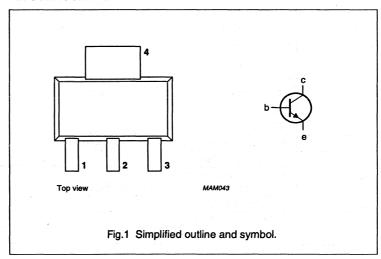

| PMBTA42; PMBTA43                       | Silicon epitaxial transistor                          | 453  |

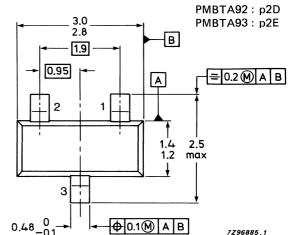

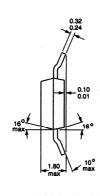

| PMBTA92; PMBTA93                       | Silicon epitaxial transistor                          | 456  |

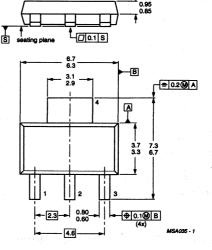

| PZTA42; PZTA43                         | Silicon epitaxial transistor                          | 458  |

| PZTA44; PZTA45                         | NPN high-voltage transistor                           | 461  |

| PZTA92; PZTA93                         | Silicon epitaxial transistor                          | 464  |

| VN2406L                                | N-channel enhancement mode vertical D-MOS transistor  | 868  |

| LCD DRIVERS AND MOC                    | IROCONTROLLER PERIPHERALS                             |      |

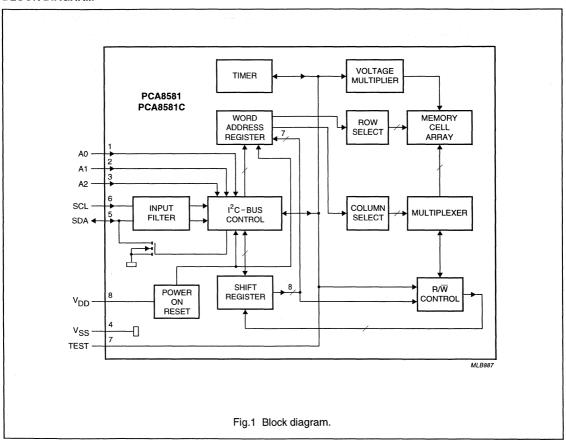

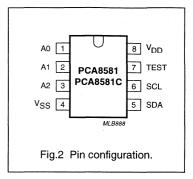

| PCA8581; PCA8581C                      | 128 x 8-bit EEPROM with I2C-bus interface             | 138  |

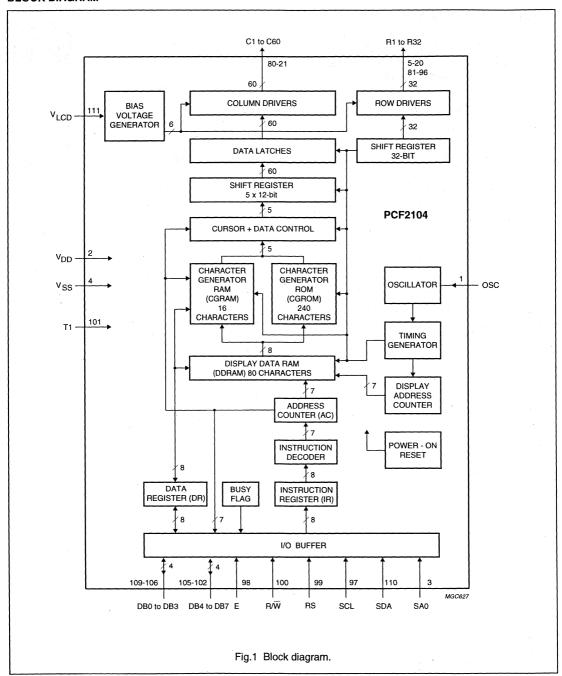

| PCF2104 family                         | LCD controller/drivers                                | 417  |

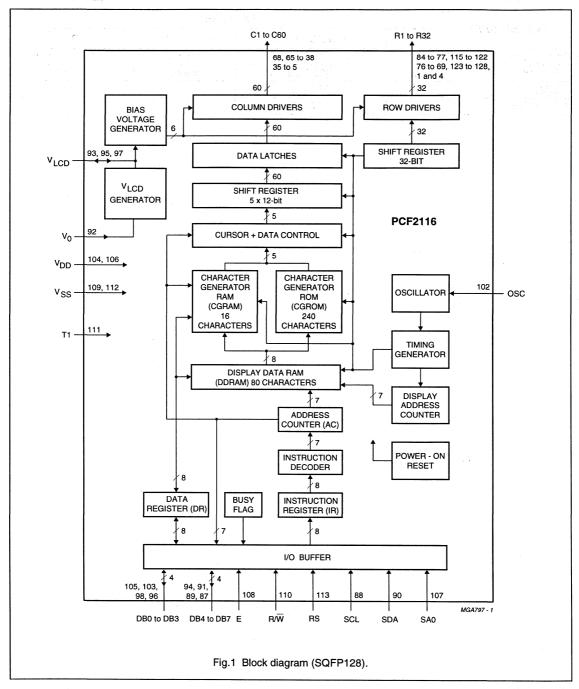

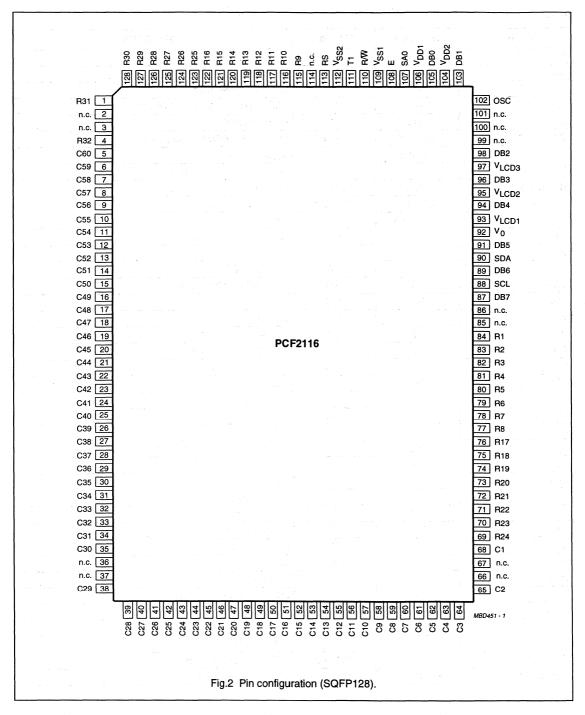

| PCF2116 family<br>(PCF2114X; PCF2116X) | LCD controller/drivers                                | 420  |

| PCF8566                                | Universal LCD driver for low multiplex rates          | 435  |

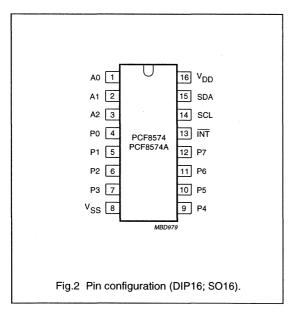

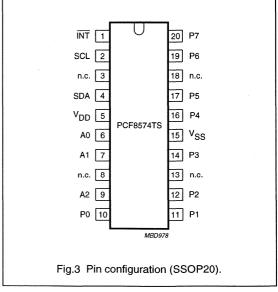

| PCF8574                                | Remote 8-bit I/O expander for I2C-bus                 | 438  |

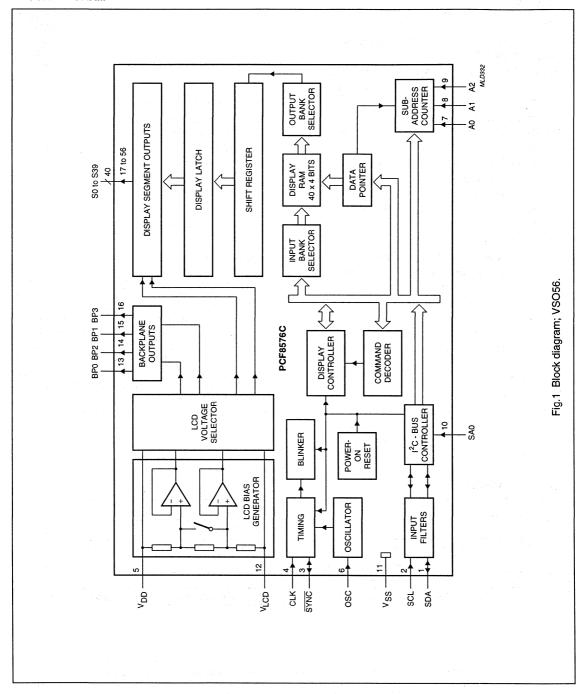

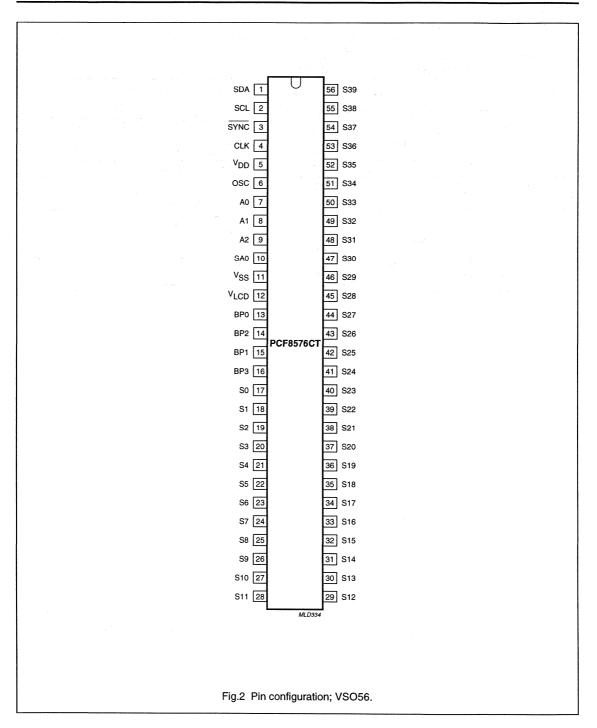

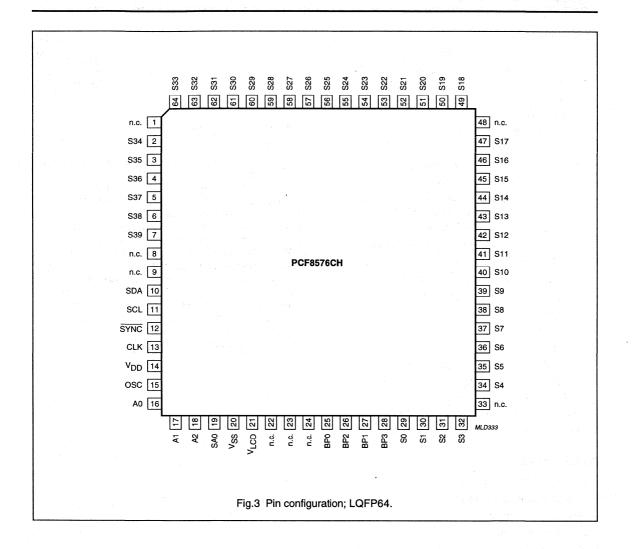

| PCF8576C                               | Universal LCD driver for low multiplex rates          | 441  |

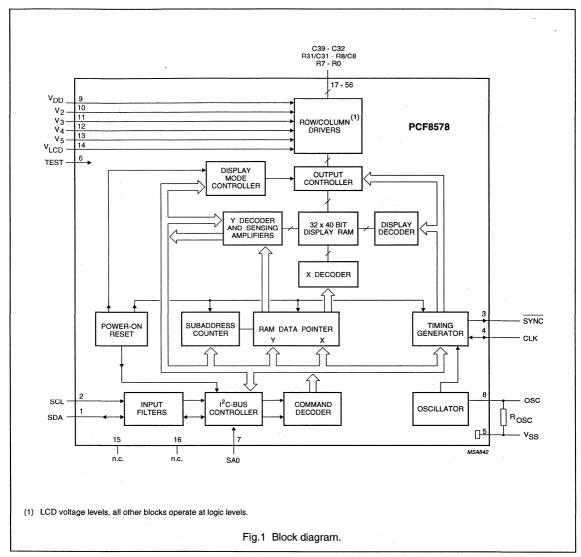

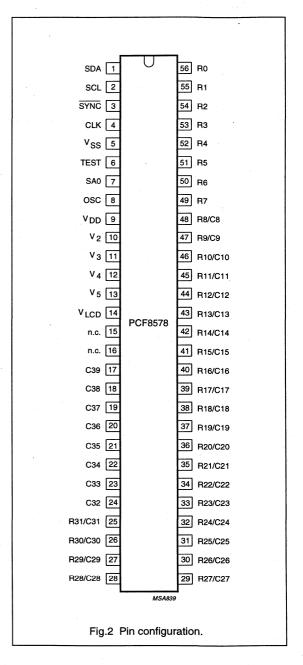

| PCF8578                                | LCD row/column driver for dot matrix graphic displays | 446  |

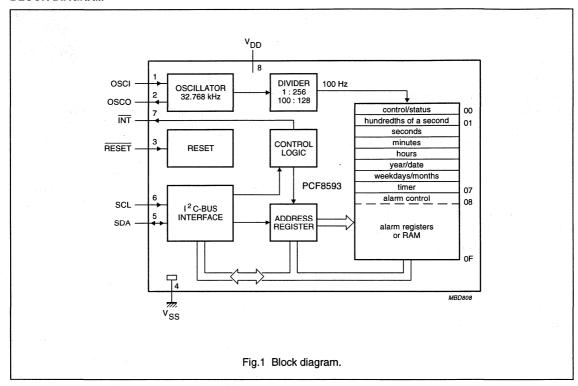

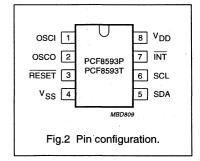

| PCF8593                                | Low power clock calendar                              | 449  |

|                                        |                                                       |      |

1996 Aug 19 8

# Alphanumeric index

# Selection guide

|                      |                                                        | PAGE                                                                                                           |

|----------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| BC327; BC327A; BC328 | Silicon planar epitaxial transistor                    | 58                                                                                                             |

| BC337; BC337A; BC338 | Silicon planar epitaxial transistor                    | 59                                                                                                             |

| BC546; BC547; BC548  | Silicon planar epitaxial transistor                    | 60                                                                                                             |

| BC556; BC557; BC558  | Silicon planar epitaxial transistor                    | 61                                                                                                             |

| BC846; BC847; BC848  | Silicon planar epitaxial transistor                    | 62                                                                                                             |

| BC856/7/8            | Silicon planar epitaxial transistors                   | 63                                                                                                             |

| BR211 series         | Breakover diodes                                       | 64                                                                                                             |

| BS107                | N-channel enhancement mode vertical D-MOS transistor   | 65                                                                                                             |

| BS107A               | N-channel enhancement mode vertical D-MOS transistor   | 66                                                                                                             |

| BS108                | N-channel enhancement mode vertical D-MOS transistor   | 67                                                                                                             |

| BS170                | N-channel vertical D-MOS transistor                    | 68                                                                                                             |

| BSN10; BSN10A        | N-channel enhancement mode vertical D-MOS transistor   | 69                                                                                                             |

| BSN20                | N-channel enhancement mode vertical D-MOS transistor   | 70                                                                                                             |

| BSN254; BSN254A      | N-channel enhancement mode vertical D-MOS transistor   | , , , , , , , , , , , , , , <b>7</b> 1                                                                         |

| BSN274; BSN274A      | N-channel enhancement mode vertical D-MOS transistor   | 72                                                                                                             |

| BSN304; BSN304A      | N-channel enhancement mode vertical D-MOS transistor   | 73                                                                                                             |

| BSP126               | N-channel enhancement mode vertical D-MOS transistor   | 74                                                                                                             |

| BSP130               | N-channel enhancement mode vertical D-MOS transistor   | 75                                                                                                             |

| BSP145               | N-channel enhancement mode vertical D-MOS transistor   | 76                                                                                                             |

| BSP225               | P-channel enhancement mode vertical D-MOS transistor   | 77                                                                                                             |

| BSP254; BSP254A      | P-channel enhancement mode vertical D-MOS transistor   | 78                                                                                                             |

| BSP304; BSP304A      | P-channel enhancement mode vertical D-MOS transistor   | 79                                                                                                             |

| BSP92                | P-channel enhancement mode vertical D-MOS transistor   | 80                                                                                                             |

| BSS89                | N-channel enhancement mode vertical D-MOS transistor   | 81 a 81                                                                                                        |

| BSS92                | P-channel enhancement mode vertical D-MOS transistor   | 1 1 <sub>2</sub> 25 3 2 3 3 <b>82</b>                                                                          |

| BST124               | N-channel depletion mode vertical D-MOS transistor     | 83 a sa 1965 a sa 19 |

| BST74A               | N-channel vertical D-MOS transistor                    | : -, -, -: 1 : : : : : : : : : : : : : : : : :                                                                 |

| BZW03 series         | Regulator diodes                                       | 85                                                                                                             |

| BZW14                | Transient suppressor diode                             | 86                                                                                                             |

| MPSA42; MPSA43       | High-voltage silicon planar transistor                 | 87                                                                                                             |

| MPSA44; MPSA45       | NPN high-voltage transistor                            | 88                                                                                                             |

| MPSA92; MPSA93       | High-voltage silicon planar transistor                 | **                                                                                                             |

| NE/SE567             | Tone decoder/phase-locked loop                         | 90                                                                                                             |

| NE5900               | Call progress decoder                                  | 103                                                                                                            |

| PCA1070              | Multistandard programmable analog CMOS transmission IC | 110                                                                                                            |

| PCA8581; PCA8581C    | 128 x 8-bit EEPROM with I2C-bus interface              | 138                                                                                                            |

| PCD3310 family       | Pulse and DTMF dialler with redial                     | 141                                                                                                            |

| PCD3311C; PCD3312C   | DTMF/modem/musical-tone generators                     | 159                                                                                                            |

| PCD3330              | Multistandard repertory dialler/ringer with EEPROM     | 176                                                                                                            |

| PCD3332-X family     | Multistandard pulse/tone repertory dialler/ringer      | 179                                                                                                            |

1996 Aug 19

# Alphanumeric index

# Selection guide

|                                       |                                                                                                                 | PAGE |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|

| PCD3344A; PCD3349A                    | 8-bit microcontroller with DTMF generator                                                                       | 201  |

| PCD3350A                              | 8-bit microcontroller with DTMF generator and 256 bytes EEPROM and real-time clock                              | 215  |

| PCA3351C/52C/53C;<br>PCD3351A/52A/53A | 8-bit microcontroller with DTMF generator and 128 bytes EEPROM                                                  | 246  |

| PCD3354A/54C                          | 8-bit microcontroller with DTMF generator and 256 bytes EEPROM                                                  | 271  |

| PCD3356A/57A/59A                      | 8-bit microcontroller with DTMF generator and 128 bytes EEPROM                                                  | 296  |

| PCD3360                               | Programmable multi-tone telephone ringer                                                                        | 321  |

| PCD33XXA Family                       | 8-bit telecom microcontroller                                                                                   | 334  |

| PCD3755X                              | 8-bit microcontroller with DTMF generator, 8 kbytes OTP and 128 bytes EEPROM                                    | 362  |

| PCD3756X                              | 8-bit microcontroller with DTMF generator, 8 kbytes OTP and 128 bytes EEPROM                                    | 386  |

| PCD4440T                              | Analog voice scrambler/descrambler                                                                              | 411  |

| PCF2104 family                        | LCD controller/drivers                                                                                          | 417  |

| PCF2116 family                        | LCD controller/drivers                                                                                          | 420  |

| PCF84C12A/22A/42A                     | 8-bit microcontroller                                                                                           | 425  |

| PCF8566                               | Universal LCD driver for low multiplex rates                                                                    | 435  |

| PCF8574                               | Remote 8-bit I/O expander for I2C-bus                                                                           | 438  |

| PCF8576C                              | Universal LCD driver for low multiplex rates                                                                    | 441  |

| PCF8578                               | LCD row/column driver for dot matrix graphic displays                                                           | 446  |

| PCF8593                               | Low power clock calendar                                                                                        | 449  |

| PMBF107                               | P-channel enhancement mode vertical D-MOS transistor                                                            | 451  |

| PMBF170                               | N-channel enhancement mode vertical D-MOS transistor                                                            | 452  |

| PMBTA42; PMBTA43                      | Silicon epitaxial transistor                                                                                    | 453  |

| PMBTA92; PMBTA93                      | Silicon epitaxial transistor                                                                                    | 456  |

| PZTA42; PZTA43                        | Silicon epitaxial transistor                                                                                    | 458  |

| PZTA44; PZTA45                        | NPN high-voltage transistor                                                                                     | 461  |

| PZTA92; PZTA93                        | Silicon epitaxial transistor                                                                                    | 464  |

| TDA7050                               | Low voltage mono/stereo power amplifier                                                                         | 466  |

| TDA7050T                              | Low voltage mono/stereo power amplifier                                                                         | 471  |

| TDA7052 A/AT                          | 1 W BTL mono audio amplifier                                                                                    | 475  |

| TEA1060; TEA1061                      | Versatile telephone transmission circuits with dialler interface                                                | 483  |

| TEA1062; TEA1062A                     | Low-voltage transmission circuit with dialler interface                                                         | 500  |

| TEA1064A                              | Low voltage versatile telephone transmission circuit with dialler interface and transmit level dynamic limiting | 521  |

| TEA1064B                              | Low voltage versatile telephone transmission circuit with dialler interface and transmit level dynamic limiting | 549  |

| TEA1065                               | Versatile telephone transmission circuit with dialler interface                                                 | 576  |

| TEA1066T                              | Versatile telephone transmission circuit with dialler interface                                                 | 595  |

| TEA1067                               | Low voltage versatile telephone transmission circuit with dialler interface                                     | 613  |

| TEA1068                               | Versatile telephone transmission circuit with dialler interface                                                 | 632  |

1996 Aug 19

# Alphanumeric index

# Selection guide

|                   |                                                                             | PAGE |

|-------------------|-----------------------------------------------------------------------------|------|

| TEA1069N          | Versatile speech/dialler/ringer with music-on-hold                          | 649  |

| TEA1081           | Supply circuit with power-down for telephone set peripherals                | 680  |

| TEA1083; TEA1083A | Call progress monitor for line powered telephone sets                       | 687  |

| TEA1085; TEA1085A | Listening-in circuit for line powered telephone sets                        | 699  |

| TEA1093           | Hands-free IC                                                               | 722  |

| TEA1094; TEA1094A | Hands-free IC                                                               | 744  |

| TEA1095           | Noise switched speakerphone IC                                              | 763  |

| TEA1096; 1096A    | Speech and listening-in IC                                                  | 781  |

| TEA1112; TEA1112A | Low voltage versatile transmission circuits with dialler interface          | 807  |

| TEA1113           | Low voltage versatile telephone transmission circuit with dialler interface | 821  |

| TEA1118; TEA1118A | Versatile cordless transmission                                             | 835  |

| UBA1702; UBA1702A | Line interrupter driver and ringer                                          | 850  |

| VN2406L           | N-channel enhancement mode vertical D-MOS transistor                        | 868  |

| 2N5400; 2N5401    | Silicon PNP high-voltage transistor                                         | 869  |

| 2N5550; 2N5551    | Silicon NPN high-voltage transistor                                         | 870  |

| 2N7000            | N-channel enhancement mode vertical D-MOS transistor                        | 871  |

| 2N7002            | N-channel vertical D-MOS transistor                                         | 872  |

# Replacement list

# Selection guide

# REPLACEMENT/WITHDRAWAL TYPES

The following type numbers were in the previous issue of this data handbook, but not in the current version:

| TYPE NUMBER        | REPLACED BY | REASON FOR DELETION |

|--------------------|-------------|---------------------|

| CT914; CT918       |             | Transferred to IC17 |

| MC3361             |             | Discontinued        |

| NE570/571/SA571    |             | Transferred to IC17 |

| NE/SA572           |             | Transferred to IC17 |

| NE/SA575           |             | Transferred to IC17 |

| NE/SA576           |             | Transferred to IC17 |

| NE/SA577           |             | Transferred to IC17 |

| NE/SA578           |             | Transferred to IC17 |

| NE/SA600           |             | Transferred to IC17 |

| NE/SA602A          | 34.5        | Transferred to IC17 |

| NE/SA604A          |             | Transferred to IC17 |

| NE/SA605           |             | Transferred to IC17 |

| NE/SA612A          |             | Transferred to IC17 |

| NE/SA614A          |             | Transferred to IC17 |

| NE/SA615           |             | Transferred to IC17 |

| NE/SA624           |             | Transferred to IC17 |

| NE/SA625           |             | Transferred to IC17 |

| NE/SA627           |             | Transferred to IC17 |

| NE/SA630           |             | Transferred to IC17 |

| NE/SA5200          |             | Transferred to IC17 |

| NE/SA/SE5205A      |             | In IC11             |

| NE/SA5209          |             | Transferred to IC17 |

| NE/SA5219          |             | Transferred to IC17 |

| NE/SA5234          |             | In IC11             |

| NE/SA5750          |             | Transferred to IC17 |

| NE/SA5751          |             | Transferred to IC17 |

| OM4031T            |             | Transferred to IC17 |

| OM5300             |             | discontinued        |

| OM5301             |             | discontinued        |

| OM5302             |             | discontinued        |

| PCA5000AT          |             | Transferred to IC17 |

| PCD332XC family    |             | discontinued        |

| PCD3315A           |             | discontinued        |

| PCD3343A; PCD3348A |             | discontinued        |

| PCD3346            |             | discontinued        |

| PCD3347            |             | discontinued        |

| PCD5002            |             | Transferred to IC17 |

| PCD5003            |             | Transferred to IC17 |

| PCD5032            |             | Transferred to IC17 |

# Replacement list

# Selection guide

| TYPE NUMBER     | REPLACED BY | REASON FOR DELETION |

|-----------------|-------------|---------------------|

| PCD5040/PCD5041 |             | Transferred to IC17 |

| PCF5001         |             | Transferred to IC17 |

| PCF5075         |             | Transferred to IC17 |

| PCF5081         |             | Transferred to IC17 |

| PCF5083         |             | Transferred to IC17 |

| PCF8591         |             | In IC12             |

| SA601           |             | Transferred to IC17 |

| SA606           |             | Transferred to IC17 |

| SA607           |             | Transferred to IC17 |

| SA608           |             | Transferred to IC17 |

| SA616           |             | Transferred to IC17 |

| SA617           |             | Transferred to IC17 |

| SA620           |             | Transferred to IC17 |

| SA626           |             | Transferred to IC17 |

| SA636           |             | Transferred to IC17 |

| SA637           |             | Transferred to IC17 |

| SA639           |             | Transferred to IC17 |

| SA701           |             | Transferred to IC17 |

| SA702           |             | Transferred to IC17 |

| SA703           |             | Transferred to IC17 |

| SA900           |             | Transferred to IC17 |

| SA1620          |             | Transferred to IC17 |

| SA1638          |             | Transferred to IC17 |

| SA5752          |             | Transferred to IC17 |

| SA5753          |             | Transferred to IC17 |

| SA7025          |             | Transferred to IC17 |

| SA8025          |             | Transferred to IC17 |

| SAA1500T        |             | Transferred to IC17 |

| SAA1501T        |             | Transferred to IC17 |

| TDA1010A        |             | In IC01             |

| TDA1011         |             | In IC01             |

| TDA1015T        |             | In IC01             |

| TDA1576T        |             | In IC01             |

| TDA8041H        |             | In IC02             |

| TDA8568         |             | discontinued        |

| TDA8569         |             | discontinued        |

| TDA8579         |             | discontinued        |

| TDA8780M        |             | Transferred to IC17 |

| TDA8781T        |             | discontinued        |

| TDD1742T        |             | Transferred to IC17 |

| TEA1041T        |             | Transferred to IC17 |

# Replacement list

# Selection guide

| TYPE NUMBER       | REPLACED BY | REASON FOR DELETION |

|-------------------|-------------|---------------------|

| TEA1088T          |             | Transferred to IC17 |

| TEA1100; TEA1100T |             | Transferred to IC17 |

| TEA1101; TEA1101T |             | Transferred to IC17 |

| TEA1102           |             | Transferred to IC17 |

| TEA1104           |             | Transferred to IC17 |

| UAA2050T          |             | Transferred to IC17 |

| UAA2072M          |             | Transferred to IC17 |

| UAA2073AM         |             | Transferred to IC17 |

| UAA2073M          |             | Transferred to IC17 |

| UAA2076G          |             | Transferred to IC17 |

| UAA2077AM         |             | Transferred to IC17 |

| UAA2077BM         |             | Transferred to IC17 |

| UAA2080           |             | Transferred to IC17 |

| UAA2082           |             | Transferred to IC17 |

| UMA1000LT         |             | Transferred to IC17 |

| UMA1002           |             | Transferred to IC17 |

| UMA1005T          |             | Transferred to IC17 |

| UMA1014           |             | Transferred to IC17 |

| UMA1015M          |             | Transferred to IC17 |

| UMA1016XT         |             | Transferred to IC17 |

| UMA1017M          |             | Transferred to IC17 |

| UMA1018M          |             | Transferred to IC17 |

| UMA1019AM         |             | Transferred to IC17 |

| UMA1019M          |             | Transferred to IC17 |

| UMA1020AM         |             | Transferred to IC17 |

| UMA1020M          |             | Transferred to IC17 |

| UMA1021M          |             | Transferred to IC17 |

| UMA1022           |             | Transferred to IC17 |

| UMF1000T          |             | discontinued        |

# LISTENING-IN ICS

| PRODUCT<br>TYPE | DESCRIPTION                          | SUPPLY<br>VOLTAGE<br>(V) | LINE-<br>POWERED | CONSUMPTION PD (mA) TYP. | PD             | LOUDSPEAKER<br>GAIN (dB) | R <sub>xout</sub> <sup>(1)</sup> | R <sub>xout</sub> (1) PACKAGE PAGE | PAGE |

|-----------------|--------------------------------------|--------------------------|------------------|--------------------------|----------------|--------------------------|----------------------------------|------------------------------------|------|

| TDA7050         | loudspeaker amplifier                | 1.6-6.0                  | No               | 3.2                      | 8<br>N         | 26                       | BTL                              | DIP8, SO8                          | 466  |

| TDA7052         | loudspeaker amplifier                | 3-18                     | No               | 4                        | N <sub>O</sub> | 39                       | ВТС                              | DIP8                               | 475  |

| TEA1083         | call-progress monitoring IC          | 3.0                      | Yes              | 2.5                      | No             | 35                       | SEL                              | DIP8                               | 687  |

| TEA1083A        | TEA1083 with PD                      | 3.0                      | Yes              | 2.5                      | Yes            | 35                       | SEL                              | DIP16,<br>SO16                     | 687  |

| TEA1085         | TEA1083A with dynamic                | 3.6                      | Yes              | 4.2                      | Yes            | 41                       | BTL                              | DIP24,                             | 669  |

|                 | ; Larsen level limiter and e control | adjustable               |                  |                          |                |                          |                                  | S024                               |      |

| TEA1085A        | TEA1085 with logic MITE              | 3.6                      | Yes              | 4.2                      | Yes            | 41                       | BTI                              | DIP24                              | 669  |

|                 | function instead of toggle           | adjustable               | 3                | 1                        | 3              |                          |                                  | SO24                               |      |

|                 | function                             |                          |                  |                          |                |                          |                                  |                                    |      |

| TEA1096         | speech and listening-in IC           | 3.6                      | Yes              | 2.4                      | Yes            | 35.5                     | SEL                              | DIP28,                             | 781  |

|                 |                                      | adjustable               |                  |                          |                | 2                        |                                  | SO28                               |      |

|                 |                                      | supplied by              |                  |                          |                |                          |                                  |                                    |      |

|                 |                                      | speech part              |                  |                          |                |                          |                                  |                                    |      |

| TEA1096A        | speech and listening-in IC with      | 3.6 fixed                | Yes              | 2.4                      | Yes            | 35.5                     | SEL                              | DIP28,                             | 649  |

|                 | volume control                       | supplied by              |                  |                          |                |                          |                                  | SO28                               |      |

Note

1. Bridge Tied Load; Single Ended Load.

# Listening-in and handsfree ICs

| • |   |  |

|---|---|--|

|   | l |  |

| ņ |   |  |

| 2 |   |  |

| ~ |   |  |

| - |   |  |

|                 |                                                      |                          |                  |                                       |     |                    |                            |                                  | ***************************************              |                           |      |

|-----------------|------------------------------------------------------|--------------------------|------------------|---------------------------------------|-----|--------------------|----------------------------|----------------------------------|------------------------------------------------------|---------------------------|------|

| PRODUCT<br>TYPE | DESCRIPTIO                                           | SUPPLY<br>VOLTAGE<br>(V) | LINE-<br>POWERED | CURRENT CONSUMPTION PD (dB) (dB) (dB) | В   | G <sub>v(Tx)</sub> | G <sub>v(Rx)</sub><br>(dB) | R <sub>xout</sub> <sup>(1)</sup> | R <sub>xout<sup>(1)</sup> SWITCHING RANGE (dB)</sub> | PACKAGE PAGE              | PAGE |

| TEA1093         | handsfree IC<br>combined with<br>power supply        | 3.6<br>adjustable        | Yes              | 5.5                                   | Yes | 5-25               | 3-39                       | вт.                              | 0-52                                                 | DIP28,<br>SO28            | 722  |

| TEA1094         | TEA1094 for use with external supply                 | 3.3-12                   | ON.              | 3.1                                   | 2   | No 0-31            | 0-33                       | SEL                              | 0-52                                                 | DIP28,<br>SO28            | 744  |

| TEA1094A        | TEA1094A TEA1094 with power-down                     | 3.3-12                   | ON.              | 3.1                                   | Yes | Yes 0-31           | 0-33                       | SEL                              | 0-52                                                 | DIP24,<br>SO24,<br>SSOP24 | 744  |

| ТЕА1095         | TEA1094A without 2.9-12 loudspeaker drive capability | 2.9-12                   | No               | 2.7                                   | Yes | Yes 0-40           | -14 to 26 X                |                                  | 0-52                                                 | DIP24,<br>SO24            | 763  |

Note

1. Bridge Tied Load; Single Ended Load.

# Speech/transmisson ICs

IC03

| ٥  |    |

|----|----|

| 2  |    |

|    |    |

| NO | r, |

| 2  |    |

| Ĕ  |    |

| (  | ֡  |

| L  |    |

|    |    |

|        | DESCRIPTION                                                            | V <sub>LN</sub> (V)<br>TYP@15 mA | PARALLEL<br>OPERATION | lcc<br>(mA)<br>TYP. | PD     | Gv <sub>(mic)</sub> | MICRO-<br>PHONE<br>MUTE | G <sub>v(Rx)</sub><br>(dB) | R <sub>xout<sup>(2)</sup></sub> | ∆Gv(AGC)<br>(dB)<br>TYP. | PACKAGE        | PAGE |

|--------|------------------------------------------------------------------------|----------------------------------|-----------------------|---------------------|--------|---------------------|-------------------------|----------------------------|---------------------------------|--------------------------|----------------|------|

| O E E  | low-impedance<br>microphone<br>(magnetic, dynamic)                     | 4.45                             | o<br>N                | 96.0                | Yes    | 44-60               | ON<br>N                 | 17-39                      | ВТС                             | -5.9                     | DIP18          | 483  |

| ے عامر | high-impedance<br>microphone<br>(electret)                             | 4.45                             | No<br>No              | 96.0                | Yes    | 30-46               | o<br>Z                  | 17-39                      | ВТС                             | -5.9                     | DIP18          | 483  |

| J⊢ ⊢ 0 | TEA1060 &<br>TEA1061<br>combination in SO20                            | 4.45                             | No<br>No              | 96.0                | Yes    | 30-46               | o<br>N                  | 17-39                      | BTL                             | -5.9                     | SO20           | 595  |

| 1 (0   | all microphone types                                                   | 4.45                             | No                    | 96.0                | Yes    | 44-60               | S.                      | 17-39                      | BTL                             | -5.9                     | DIP18,<br>SO20 | 632  |

| ,      | optimized for parallel phones operation                                | 3.9                              | Yes                   | -                   | Yes    | 44-52               | S.                      | 20-45                      | BTL                             | -5.9                     | DIP18;<br>SO20 | 613  |

|        | simplified TEA1067<br>(no PD, SE-receiver)                             | 4.0                              | Yes                   | 6.0                 | §.     | 44-52               | <sub>S</sub>            | 20-31                      | SEL                             | -5.8                     | DIP16,<br>SO16 | 500  |

|        | TEA1062 with inverted MUTE polarity                                    | 4.0                              | Yes                   | 6.0                 | S<br>S | 44-52               | o<br>N                  | 20-31                      | SEL                             | -5.8                     | DIP16,<br>SO16 | 500  |

|        | improved TEA1067 with Dynamic limiter, strong supply point             | 3.6                              | Yes                   | 1.3                 | Yes    | 44-52               | Yes                     | 20-45                      | ВТС                             | -6.1                     | DIP20,<br>SO20 | 521  |

|        | for DC current<br>regulation                                           | 4.45                             | No                    | 1.14                | Yes    | 30-46               | No                      | 20-45                      | ВТГ                             | -5.9                     | DIP24,<br>SO24 | 526  |

|        | TEA1064A with single-ground reference                                  | 3.5                              | Yes                   | 1.3                 | Yes    | 44-52               | Yes                     | 20-45                      | BTL                             | -6.1                     | DIP20,<br>SO20 | 549  |

|        | fully programmable<br>line interface                                   | 4.83@12 mA                       | Yes                   | 2.3                 | Yes    | 30-51               | Yes                     | -25 to 11                  | ВТ.                             | via<br>software          | DIP24,<br>SO24 | 110  |

|        | EMC optimized,<br>on-chip default<br>settings, LED<br>on-hook/off-hook | 3.65                             | Yes                   | 1.15                | No.    | 39-52               | Yes                     | 19-31                      | SEL                             | က်<br>အ                  | DIP16,<br>SO16 | 807  |

|        | indication                                                             |                                  |                       |                     |        |                     |                         |                            |                                 |                          |                |      |

# Speech/transmisson ICs

| PRODUCT<br>TYPE(1) | DESCRIPTION                         | V <sub>LN</sub> (V) PARALLEL (mA) PD GV(mic) PHONE (TYP@15 mA OPERATION TYP. (dB) MUTE | PARALLEL<br>OPERATION | lcc<br>(mA)<br>TYP. | PD | Gv(mic)<br>(dB)  | MICRO-<br>PHONE<br>MUTE | G <sub>v(R</sub><br>(dB | R <sub>xout<sup>(2)</sup></sub> | $\begin{pmatrix} \Delta G_V(AGC) \\ A_{Xout}^{(2)} & (dB) \\ TYP. \end{pmatrix} P_{I}$ | PACKAGE PAGE   | PAGE |

|--------------------|-------------------------------------|----------------------------------------------------------------------------------------|-----------------------|---------------------|----|------------------|-------------------------|-------------------------|---------------------------------|----------------------------------------------------------------------------------------|----------------|------|

| TEA1112A           | TEA1112A TEA1112 with inverted MUTE | 3.65                                                                                   | Yes                   | 1.15                | 8  | 1.15 No 39-52    | Yes                     | 19-31                   | SEL                             | -5.8                                                                                   | DIP16,<br>SO16 | 807  |

|                    | polarity                            |                                                                                        |                       |                     |    |                  |                         |                         |                                 |                                                                                        |                |      |

| TEA1113            | TEA1112A with Tx                    | 4.0                                                                                    | Yes                   | 1.3                 | ટ  | 1.3 No 39-52 Yes | Yes                     | 19-31                   | SEL                             | -5.8                                                                                   | DIP16,         | 821  |

|                    | Dynamic limiter                     | :                                                                                      |                       |                     |    |                  |                         |                         |                                 |                                                                                        | SO16           |      |

| TEA1118            | interface for                       | 3.65                                                                                   | Yes                   | 1.15 No 0-11        | ટ  |                  | N <sub>o</sub>          | 19-31                   | SEL                             | -5.8                                                                                   | SSOP16,        | 835  |

|                    | cordless, answering                 |                                                                                        |                       |                     |    |                  |                         | -                       |                                 |                                                                                        | SO14           |      |

|                    | machine and                         |                                                                                        |                       |                     |    |                  | :                       |                         |                                 |                                                                                        |                | -    |

|                    | mopom                               |                                                                                        |                       |                     |    |                  |                         |                         |                                 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                |                |      |

| TEA1118A           | TEA1118A   TEA1118 with             | 3.65                                                                                   | Yes                   | 1.15 No             | 2  | 11               | Yes                     | 19-31                   | SEL                             | -5.8                                                                                   | SSOP16,        | 835  |

|                    | DTMF input                          |                                                                                        |                       |                     |    |                  |                         |                         |                                 |                                                                                        | SO14           |      |

Devices are listed as they were initially introduced.

BridgeTied Load Sindly Ended. BridgeTied Load, Single Ended Load.

# Microcontroller selection guide

MICROCONTROLLER SELECTOR GUIDE FOR IC03

|          |                |                |        | ,   |                             |                                                                   |                     |               |

|----------|----------------|----------------|--------|-----|-----------------------------|-------------------------------------------------------------------|---------------------|---------------|

| PRODUCT  | ROM            | RAM<br>(BYTES) | EEPROM | 0/1 | OPERATING<br>VOLTAGE<br>(V) | FEATURES                                                          | PACKAGE             | MAX.<br>SPEED |

| PCD3344A | 2K             | 224            | ou     | 20  | 1.8 - 6(1)                  | DTMF                                                              | DIL/SO28            | 16 MHz        |

| PCD3349A | ¥              | 224            | ou     | 20  | 1.8 - 6(1)                  | DTMF, Melody Output                                               | DIL/SO28            | 16 MHz        |

| PCD3350A | 8K             | 256            | 256    | 34  | 1.8 - 6 <sup>(1)</sup>      | DTMF, Melody Output, Realtime<br>Clock                            | QFP44               | 16 MHz        |

| PCD3351A | 2K             | 64             | 128    | 20  | 1.8 - 6 <sup>(1)</sup>      | DTMF, Melody Output                                               | DIL/SO28,<br>QFP32  | 16 MHz        |

| PCA3351C | 2K             | 64             | 128    | 20  | 1.8 - 6 <sup>(1)</sup>      | As PCD3351A, 0-50 °C,<br>VPOR = 2.0 V, ±300 mV                    | DIL/SO28,<br>QFP32  | 16 MHz        |

| PCD3352A | X <sub>4</sub> | 128            | 128    | 20  | 1.8 - 6 <sup>(1)</sup>      | DTMF, Melody Output                                               | DIL/SO28,<br>QFP32  | 16 MHz        |

| PCA3352C | ¥4             | 128            | 128    | 20  | 1.8 - 6 <sup>(1)</sup>      | As PCD3352A, 0-50 °C,<br>VPOR = 2.0 V, ±300 mV                    | DIL/S028,<br>QFP32  | 16 MHz        |

| PCD3353A | X9             | 128            | 128    | 20  | 1.8 - 6 <sup>(1)</sup>      | DTMF, Melody Output                                               | DIL/SO28,<br>QFP32  | 16 MHz        |

| PCA3353C | ξ9             | 128            | 128    | 20  | 1.8 - 6 <sup>(1)</sup>      | As PCD3353A, 0-50 °C,<br>VPOR = 2.0 V, ±300 mV                    | DIL/SO-28,<br>QFP32 | 16 MHz        |

| PCD3354A | ¥              | 256            | 256    | 36  | 1.8 - 6(1)                  | DTMF, Melody Output                                               | QFP44               | 16 MHz        |

| PCA3354C | %<br>X         | 256            | 256    | 36  | 1.8 - 6 <sup>(1)</sup>      | As PCD3354A, 0-50 °C,<br>VPOR = 2.0 V, ±300 mV                    | QFP44               | 16 MHz        |

| PCD3355A | X8             | 128            | 128    | 20  | 1.8 - 6 <sup>(1)</sup>      | DTMF, Melody Output                                               | DIL/SO28,<br>QFP32  | 16 MHz        |

| PCD3356A | %<br>X         | 128            | 128    | 20  | 1.8 - 6 <sup>(1)</sup>      | DTMF, Melody Output                                               | DIL/SO28,<br>QFP32  | 16 MHz        |

| PCD3357A | ¥9             | 128            | 128    | 50  | 1.8 - 6 <sup>(1)</sup>      | DTMF, Melody Output                                               | DIL/SO28,<br>QFP32  | 16 MHz        |

| PCD3359A | 2K             | 64             | 128    | 50  | 1.8 - 6 <sup>(1)</sup>      | As PCD3351A + keyboard interrupt.<br>Tone disabled during ringing | DIL/SO28,<br>QFP32  | 16 MHz        |

| PCD3755X | 8K OTP         | 128            | 128    | 50  | 1.8 - 6 <sup>(1)</sup>      | OTP for 3351A/52A/53A/55A                                         | DIL/SO28,<br>QFP32  | 16 MHz        |

| PCD3756X | 8K OTP         | 128            | 128    | 50  | 1.8 - 6 <sup>(1)</sup>      | OTP for 3356A/57A/59A                                             | DIL/SO28,<br>QFP32  | 16 MHz        |

|          |                |                |        |     |                             |                                                                   |                     |               |

| PRODUCT      | ROM            | RAM<br>(BYTES) | EEPROM | 0/1 | OPERATING<br>VOLTAGE<br>(V) | FEATURES               | PACKAGE         | MAX.<br>SPEED |

|--------------|----------------|----------------|--------|-----|-----------------------------|------------------------|-----------------|---------------|

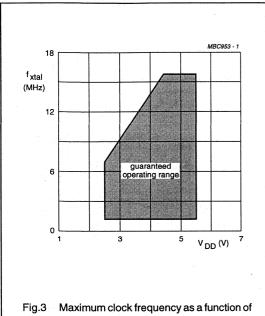

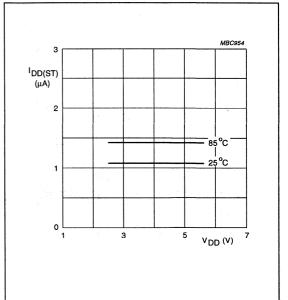

| PCF84C12A 11 | <b>1</b> X     | 64             | no     | 13  | 2.5 - 5.5                   | use external generator | DIL/SO20 16 MHz | 16 MHz        |

| PCF84C22A 2K | 2K             | 64             | no     | 13  | 2.5 - 5.5                   | use external generator | DIL/SO20        | 16 MHz        |

| PCF84C42A 4  | 4 <del>X</del> | 64 no          | ou     | 13  | 2.5 - 5.5                   | use external generator | DIL/SO20        | 16 MHz        |

Note

1. DTMF tone output and/or EEPROM erase/write from 2.5 V.

# LCD selection guide

# IC03

# LCD SEGMENT DRIVERS

| Device     | Drive | capabili<br>a Mu | ity, Nui | bility, Number of segn<br>Multiplex rate (Duty) | Drive capability, Number of segments at<br>a Multiplex rate (Duty) | ents at | Logic                  | LCD                     | Logic voltage system voltage | On-chip<br>bias | Interface            | Special                                    | Packages            | ages   | Gold   | Available |

|------------|-------|------------------|----------|-------------------------------------------------|--------------------------------------------------------------------|---------|------------------------|-------------------------|------------------------------|-----------------|----------------------|--------------------------------------------|---------------------|--------|--------|-----------|

|            | 1:1   | 1:2              | 1:3      | 1:4                                             | 1:8                                                                | 1:16    | 1:3 1:4 1:8 1:16 range | V <sub>op</sub><br>max. | current (µA) g               | voltage         |                      | rutures                                    |                     |        | sdwna  |           |

| PCF8566    | 24    | 48               | 72       | 96                                              |                                                                    |         | 2.5                    | 9                       | 15                           | yes             | l <sup>2</sup> C-bus | cascadable                                 | DIP40               | VSO40  |        | MOU       |

|            |       |                  |          |                                                 |                                                                    |         | 9.0                    |                         |                              |                 |                      | PCF8566/76                                 |                     |        |        |           |

| PCF8576    | 40    | 8                | 120      | 120 160                                         |                                                                    |         | 2.0                    | (9) 6                   | 25                           | yes             | l <sup>2</sup> C-bus | cascadable                                 | VSO56 LQFP64 on FFC | LQFP64 | on FFC | MOU       |

| <u>(</u> ) |       |                  |          |                                                 |                                                                    |         | 9.0 (6)                |                         |                              |                 |                      | PCF8566/76                                 |                     |        |        |           |

| PCF8578    |       |                  |          |                                                 | 256                                                                | 384     | 2.5                    | 6                       | 250(1)                       | 2               | l <sup>2</sup> C-bus | 12C-bus easy blinking, VSO56 LQFP64 on FFC | VSO56               | LQFP64 | on FFC | MOU       |

|            |       |                  |          |                                                 |                                                                    |         | <b>£</b>               |                         |                              |                 |                      | scratch pad                                |                     |        |        |           |

|            |       |                  |          |                                                 |                                                                    |         | 0                      |                         |                              |                 |                      | BAM                                        |                     |        |        |           |

# Note

1. Including external bias generator.

# GRAPHIC LCD DRIVERS

| Available                                                         | now                                              | Mow                                                                    |

|-------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------|

|                                                                   | င့                                               | <u>-</u><br>ي                                                          |

| Gold<br>Bumps                                                     | on FF                                            | on FF                                                                  |

| Packages                                                          | LQFP64                                           | LQFP64                                                                 |

| Pac                                                               | VSO56                                            | VSO56                                                                  |

| Special                                                           | PC-bus for mux VSO56 LQFP64 on FFC 1:8,16, 24,32 | I <sup>2</sup> C-bus for mux VSO56 LQFP64 on FFC r<br>1:8,16,<br>24,32 |

| Interface                                                         | l <sup>2</sup> C-bus                             | l <sup>2</sup> C-bus                                                   |

| On-chip<br>bias<br>voltage<br>multiplier                          | ou                                               | ou                                                                     |

| Matrix Logic voltage system bias size range max. (μΑ) generator m | ou                                               |                                                                        |

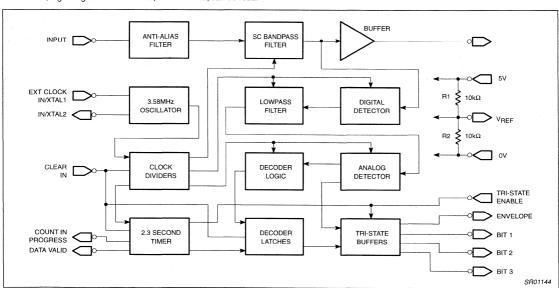

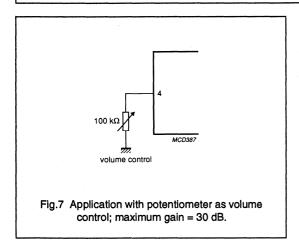

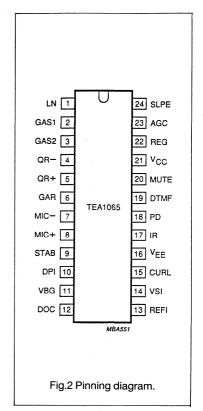

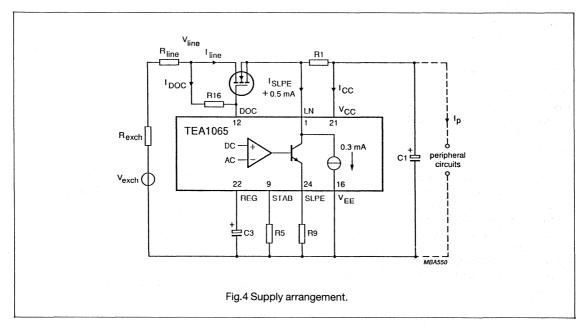

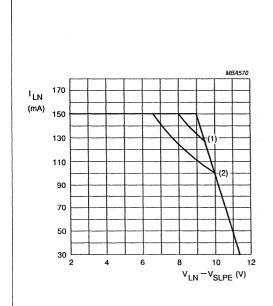

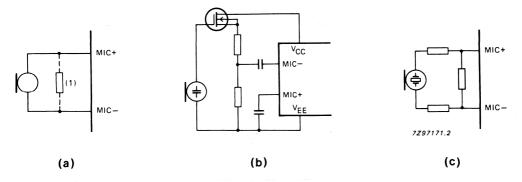

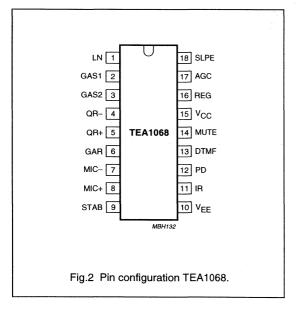

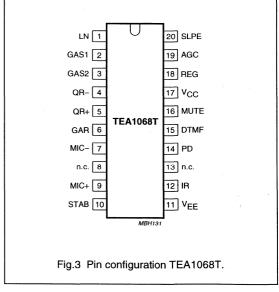

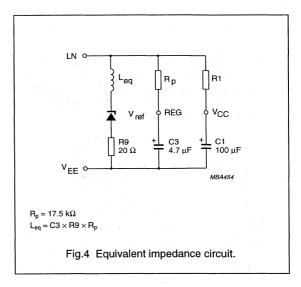

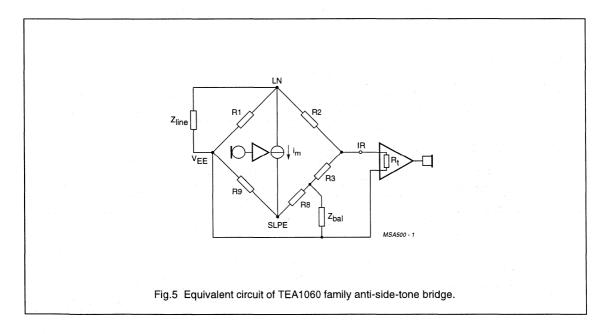

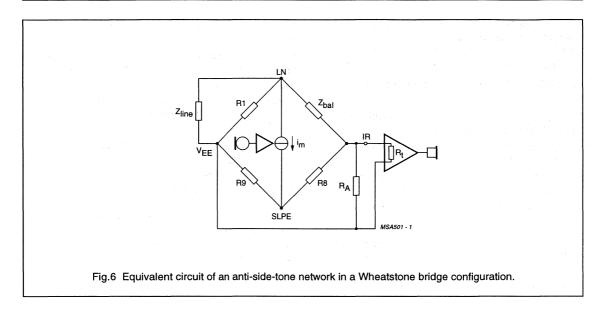

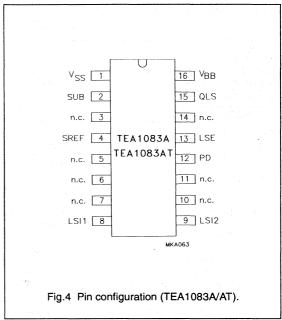

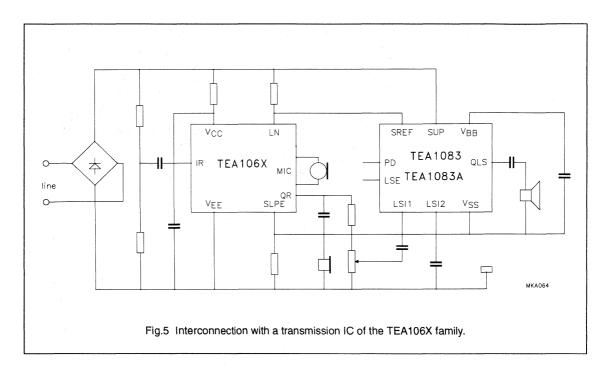

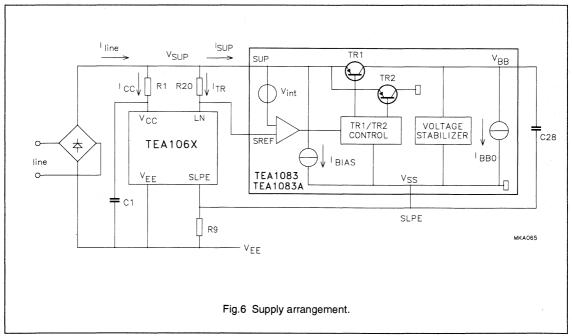

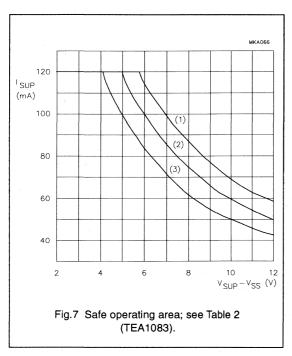

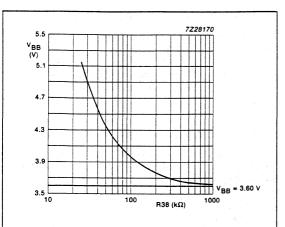

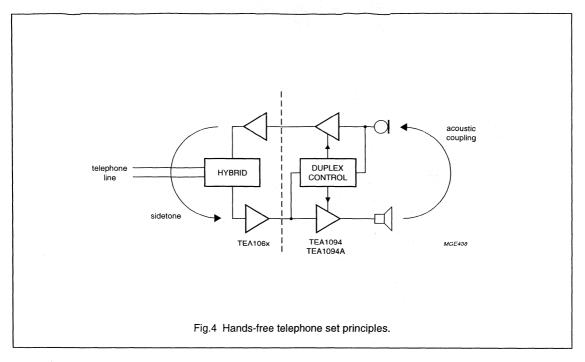

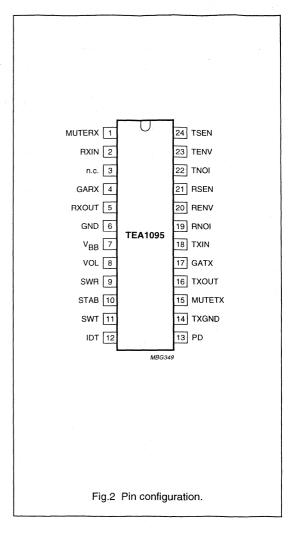

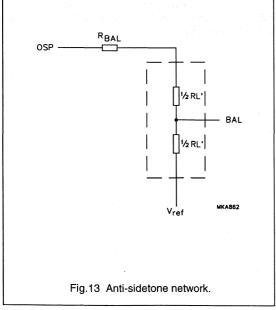

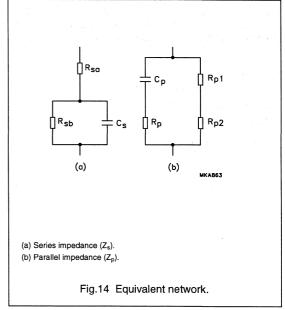

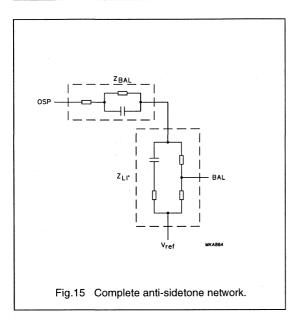

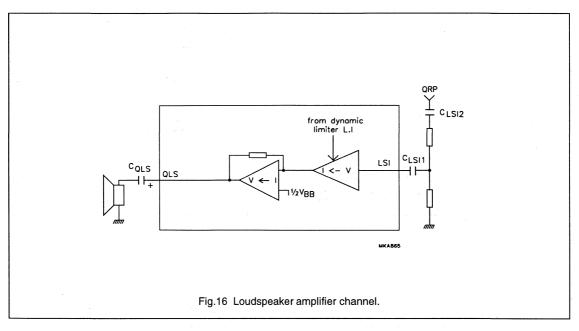

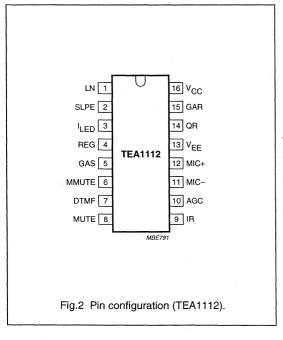

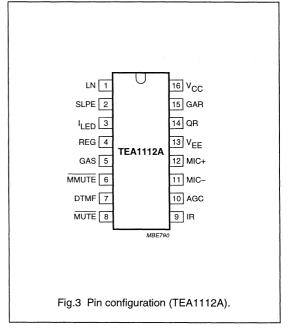

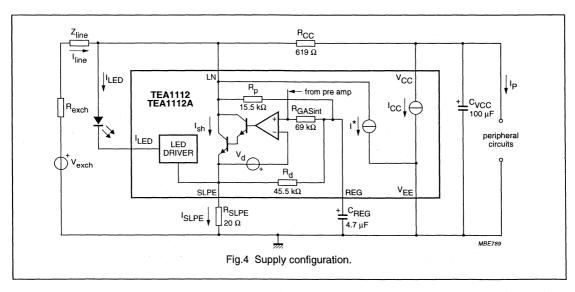

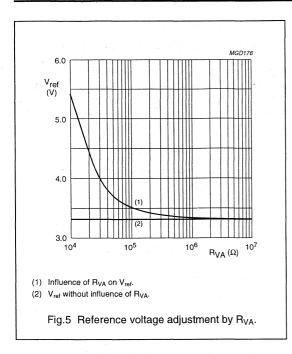

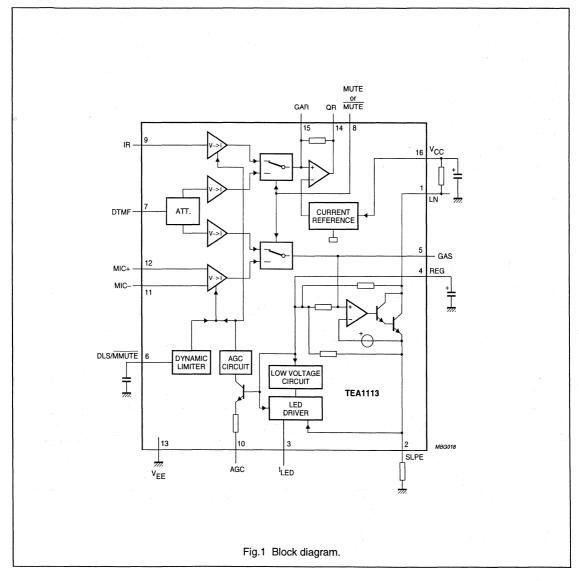

| Typ. system current (µA)                                          | 250(1)                                           | 6                                                                      |